P4C164LL-80P6C データシートの表示(PDF) - Semiconductor Corporation

部品番号

コンポーネント説明

一致するリスト

P4C164LL-80P6C Datasheet PDF : 10 Pages

| |||

P4C164LL - VERY LOW POWER 8K x 8 STATIC CMOS RAM

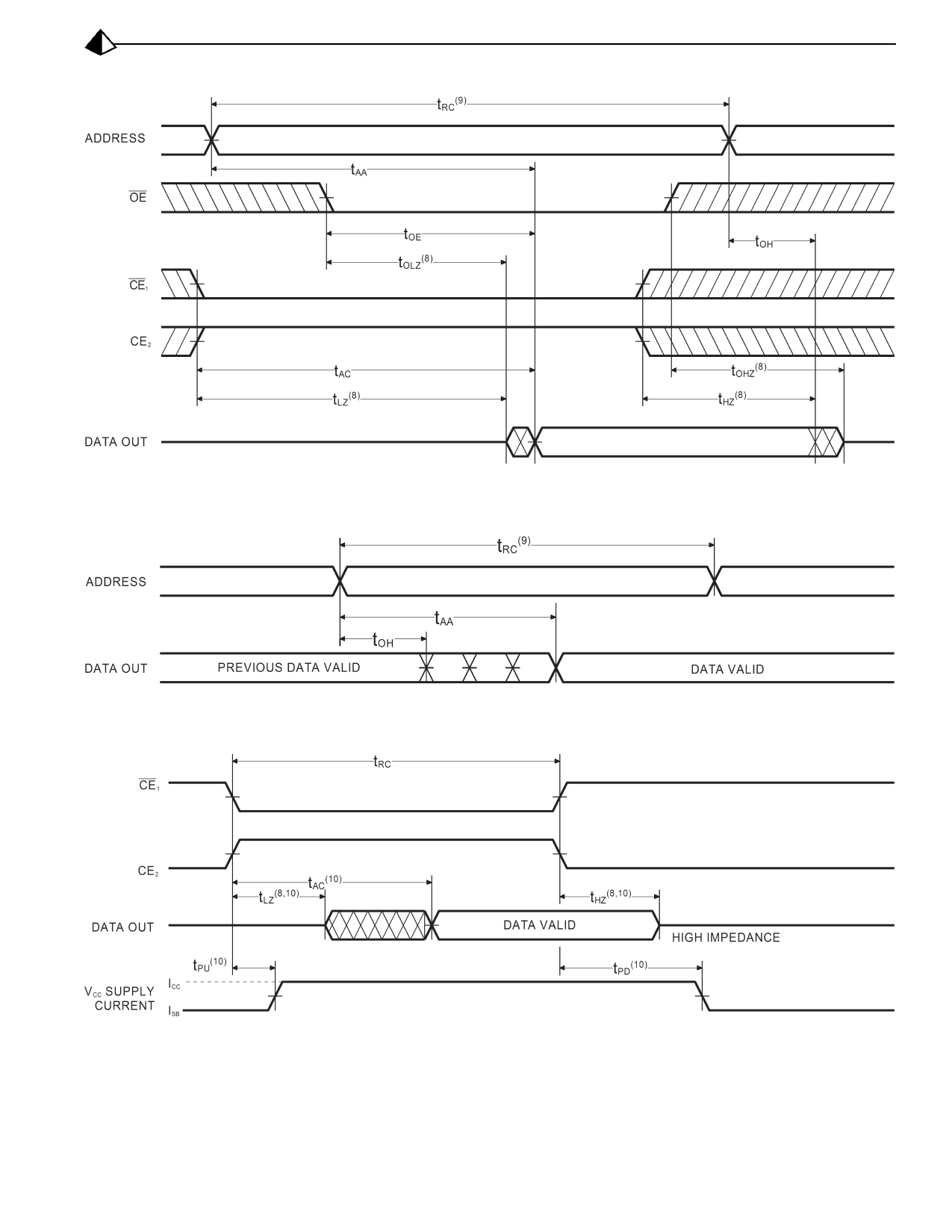

TIMING WAVEFORM OF READ CYCLE NO. 1 (OE CONTROLLED)(1)

TIMING WAVEFORM OF READ CYCLE NO. 2 (ADDRESS CONTROLLED)

TIMING WAVEFORM OF READ CYCLE NO. 3 (CE1, CE2 CONTROLLED)

Notes:

5. WE is HIGH for READ cycle.

6.

7.

CE1 is LOW, CE2 is

ADDRESS must be

HIGH and OE is LOW for READ cycle.

valid prior to, or coincident with CE1 transition

LOW

and CE2 transition HIGH.

8. Transition is measured ± 200 mV from steady state voltage prior to

change, with loading as specified in Figure 1. This parameter is sampled

and not 100% tested.

Document # SRAM116 REV 04

9. Read Cycle Time is measured from the last valid address to the first

transitioning address.

10. Transitions caused by a chip enable control have similar delays ir-

respective of whether CE1 or CE2 causes them.

Page 4