DG9051(2005) データシートの表示(PDF) - Vishay Semiconductors

部品番号

コンポーネント説明

一致するリスト

DG9051

(Rev.:2005)

(Rev.:2005)

DG9051 Datasheet PDF : 12 Pages

| |||

DG9051/9052/9053

Vishay Siliconix

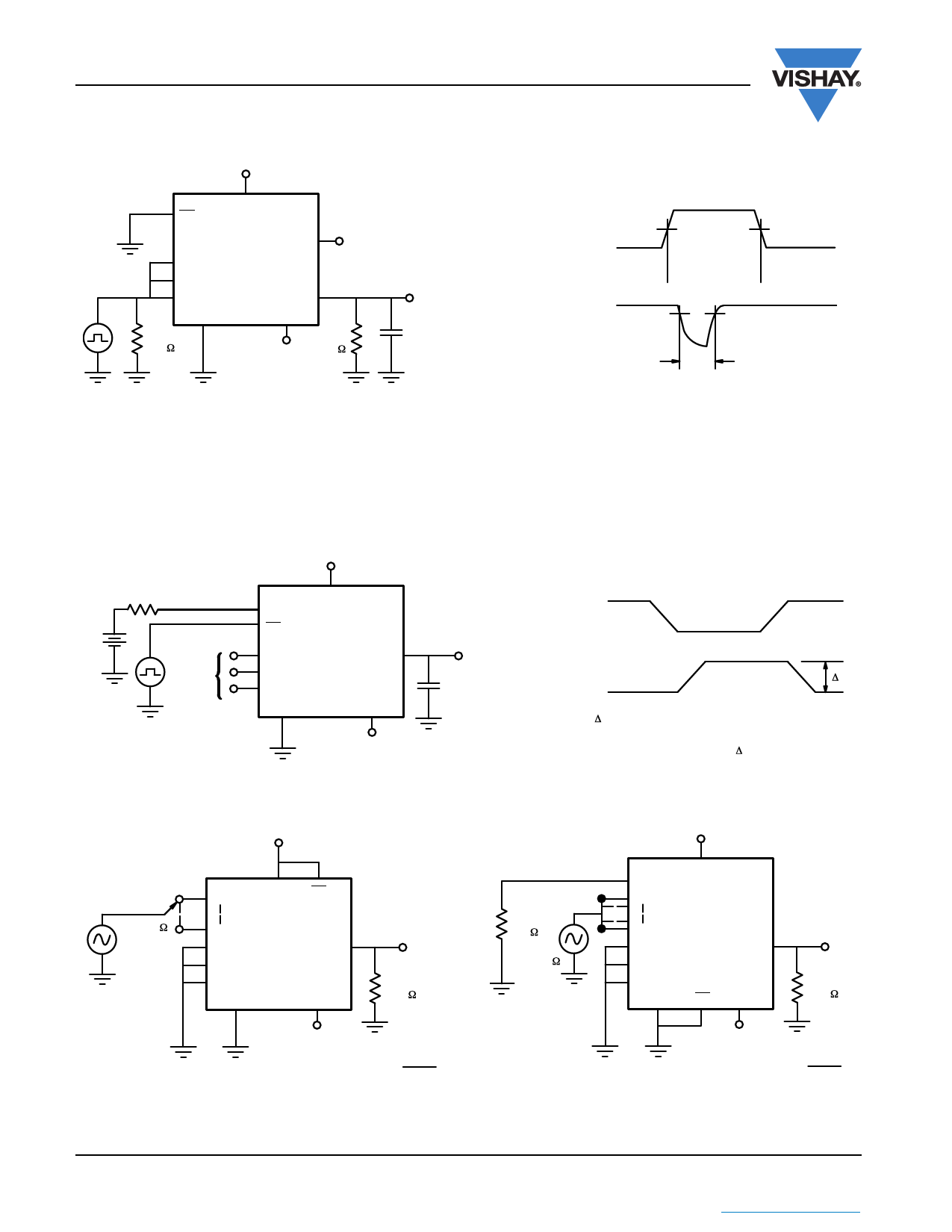

TEST CIRCUITS

New Product

V+

EN

All S and Da

VS1

A0

A1

A2

Db, D

GND

V–

50 Ω

V– 300 Ω

VO

35 pF

Logic

3V

Input

0V

VS

Switch

Output

VO

0V

50%

tr <5 ns

tf <5 ns

90%

tOPEN

Rg

Vg

Channel

Select

Figure 3. Break-Before-Make Interval

Return to Specifications:

Single Supply 12 V

Dual Supply V+ = 5 V, V– = –5 V

Single Supply 5 V

Single Supply 3 V

V+

V+

SX

EN

A0

A1

A2

GND

D

V–

V–

VO

CL

1 nF

Logic 3 V

Input

OFF

ON

0V

OFF

Switch

Output

∆ VO

∆VO is the measured voltage due to charge transfer

error Q, when the channel turns off.

Q = CL x ∆VO

Figure 4. Charge Injection

V+

VIN

Rg = 50 Ω

SX

V+

S8

A0

A1

A2

GND

EN

D

V–

VOUT

RL

50 Ω

V–

Off Isolation = 20 log

Figure 5. Off Isolation

VOUT

VIN

V+

VIN

RIN

50 Ω

Rg = 50 Ω

V+

S1

SX

S8

A0

D

A1

A2

GND EN V–

VOUT

RL

50 Ω

V–

Crosstalk = 20 log

Figure 6. Crosstalk

VOUT

VIN

www.vishay.com

10

Document Number: 73410

S-52072-Rev. A, 10-Oct-05