WM8734 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

WM8734 Datasheet PDF : 45 Pages

| |||

WM8734

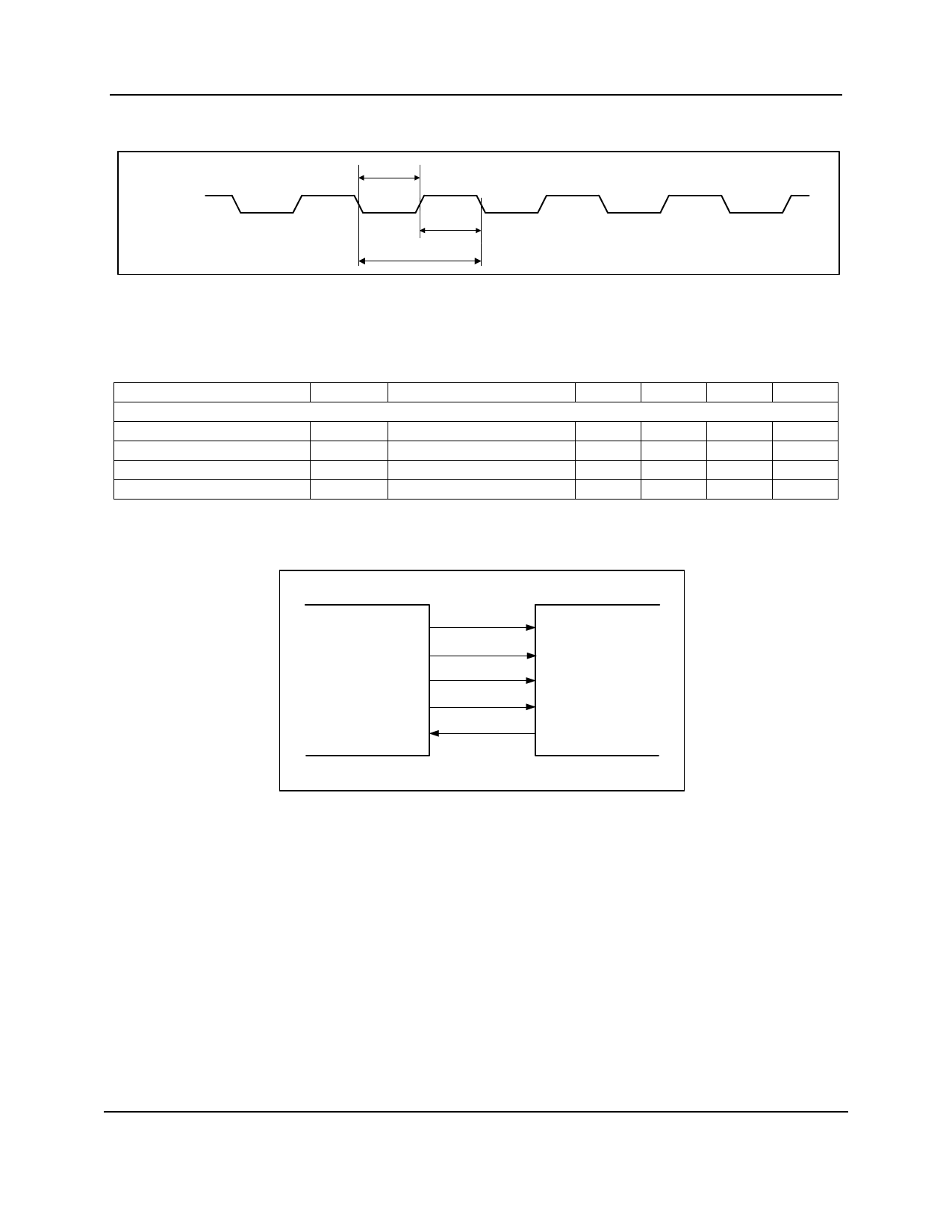

MASTER CLOCK TIMING

MCLK

t MCLKL

t MCLKH

t MCLKY

Production Data

Figure 1 System Clock Timing Requirements

Test Conditions

AVDD, DBVDD = 3.3V, AGND = 0V, DCVDD = 3.3V, DGND = 0V, TA = +25oC, Slave Mode, fs = 48kHz, MCLK = 256fs unless

otherwise stated.

PARAMETER

SYMBOL

System Clock Timing Information

MCLK System clock pulse width high

MCLK System clock pulse width low

MCLK System clock cycle time

TXTIH

TXTIL

TXTIY

MCLK Duty cycle

TEST CONDITIONS

MIN

18

18

54

40:60

TYP

MAX

60:40

UNIT

ns

ns

ns

DIGITAL AUDIO INTERFACE – MASTER MODE

BCLK

ADCLRC

WM8734

CODEC

DACLRC

ADCDAT

DACDAT

DSP

ENCODER/

DECODER

Figure 2 Master Mode Connection

w

PD, Rev 4.4, August 2013

9