NJU3101D データシートの表示(PDF) - Japan Radio Corporation

部品番号

コンポーネント説明

一致するリスト

NJU3101D Datasheet PDF : 22 Pages

| |||

NJU3101

Mnemonic

Operation

code

Function

Status Cycle

Memo

JPL addr 68−6F ST=1:PC←addr, ST=0:No branch

1

2 2byte Mnemonic

JMP addr C0−FF ST=1:PC←addr, ST=0:No branch

1

1

CALL addr 60−67 ST=1:(SP)←PC+2, SP←SP+1, PC←addr 1

2 2byte Mnemonic

ST=0:No branch

RET

2B PC←(SP), SP←SP-1

1

1

SBIT b

30−33 M(X,Y)b←1

1

1 B=0−3

RBIT b

TBIT b

34−37 M(X,Y)b←0

38−3B ST←M(X,Y)b

1

1 B=0−3

∗

1 B=0−3

TBA b

3C−3F ST←(AC)b

∗

1 B=0−3

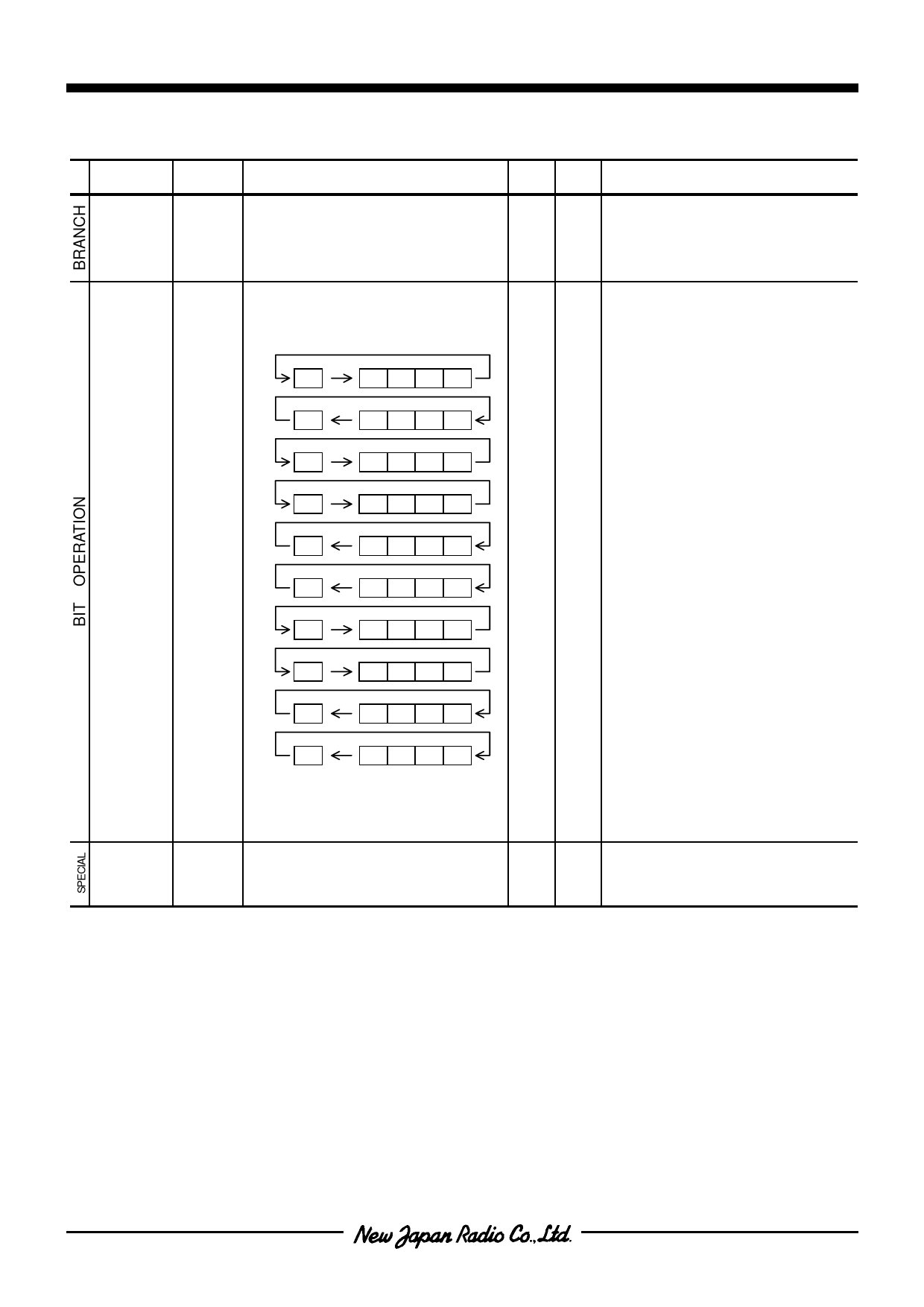

RAR

21

AC

∗

1

CY

b3 b2 b1 b0

RAL

22

AC

∗

1

CY

b3 b2 b1 b0

RYR

24

Y

CY

b3 b2 b1 b0

∗

1 RPC=0

Y’

CY

b3 b2 b1 b0

∗

1 RPC=1

RYL

25

Y

∗

1 RPC=0

CY

b3 b2 b1 b0

Y’

CY

b3 b2 b1 b0

∗

1 RPC=1

RXR

28

X

CY

b3 b2 b1 b0

∗

1 RPC=0

X’

CY

b3 b2 b1 b0

∗

1 RPC=1

RXL

29

X

∗

1 RPC=0

CY

b3 b2 b1 b0

X’

CY

b3 b2 b1 b0

∗

1 RPC=1

SEC

CLC

SRPC

RRPC

NOP

HLT

MDT

0C CY←1

1C CY←0

10 RPC←1

20 RPC←0

00 No Operation

07 CPU Halted

06 Memory Dump Test

1

1

0

1

1

1

1

1

1

1

1

1

−

−

Note)

←

∧

∨

⊕

+

-

<>

:Transfer direction

:AND

:OR

:Exclusive OR

:Add

:Subtraction

:Comparison

AC

X

X’

Y

Y’

PH

M

ROM

PC

:Accumulator

:Xregister

:X’register

:Yregister

:Y’register

:Peripheral register

:Data memory

:Program memory

:Program counter

SP

RPC

CY

ST

#K

addr

()

b

:Stack pointer

:RPC flag

:Carry flag

:Status flag

:Immediate data

:Blanch address

:A content of register or memory

pointed by the address indicated in ( ).

:Bit position

Status description)

0:After the command execution, ST-flag is always set to “0”.

1:After the command execution, ST-flag is always set to “1”.

∗:Status

- 21 -