ADNS-2051 データシートの表示(PDF) - Avago Technologies

部品番号

コンポーネント説明

一致するリスト

ADNS-2051 Datasheet PDF : 40 Pages

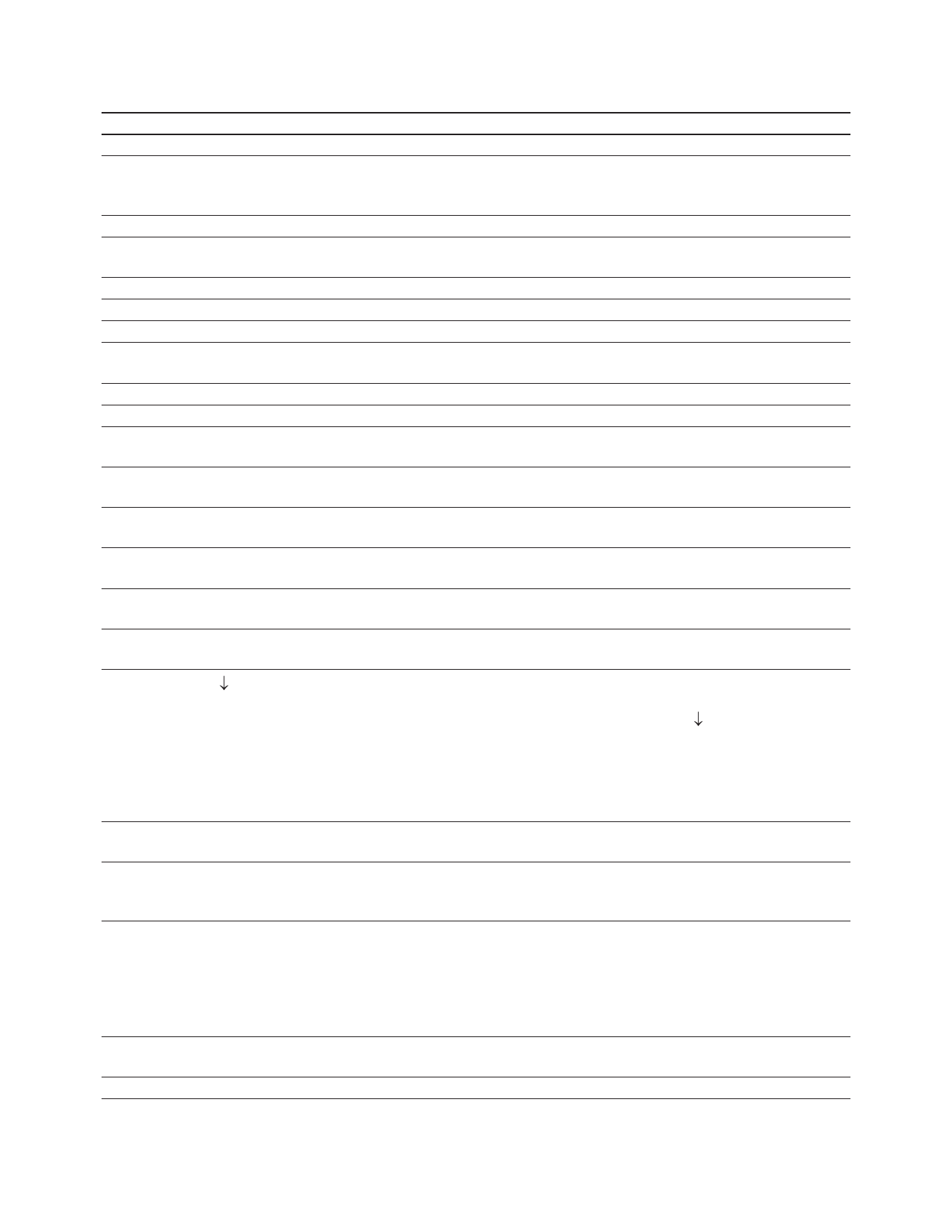

| |||

Recommended Operating Conditions

Parameter

Symbol Min. Typ. Max. Units

Operating Temperature

TA

0

40

˚C

Power Supply Voltage

VDD

4.25

5.0

5.5

volts

Power Supply Rise Time

VRT

100

ms

Supply Noise

VN

100

mV

Clock Frequency

fCLK

17.4

18.0

18.7

MHz

Serial Port Clock Frequency

SCLK

fCLK/4 MHz

Resonator Impendance

XRES

55

Ω

Distance from Lens Reference

Z

2.3

2.4

2.5

mm

Plane to Surface

Speed

S

0

14

in/sec

Acceleration

A

0.15

g

Light Level onto IC

IRRINC

80

100

25,000 mW/m2

30,000

SDIO Read Hold Time

tHOLD

100

µs

SDIO Serial Write-Write Time

tSWW

100

µs

SDIO Serial Write-Read Time

tSWR

100

µs

SDIO Serial Read-Write Time

tSRW

120

ns

SDIO Serial Read-Read Time

tSRR

120

ns

Data Delay after PD

tCOMPUTE 3.2

ms

SDIO Write Setup Time

tSETUP

60

ns

PD Pulse Width

tPDW

700

µs

(to power down the chip)

PD Pulse Width

tPDR

100

µs

(to reset the serial port)

Frame Rate

FR

1500

frames/s

Bin Resistor

R1

15 K 15 K 37 K Ω

Notes

Register values retained for

voltage transients below

4.25 V but greater than 4 V.

Peak to peak within

0-100 MHz.

Set by ceramic resonator.

Results in ±0.2 mm DOF.

(See Figure 10.)

@ frame rate = 1500/second.

@ frame rate = 1500/second.

λ = 639 nm

λ = 875 nm

Hold time for valid data.

(Refer to Figure 28.)

Time between two write

commands. (Refer to Figure 31.)

Time between write and read

operation. (Refer to Figure 32.)

Time between read and write

operation. (Refer to Figure 33.)

Time between two read

commands. (Refer to Figure 33.)

After tCOMPUTE, all registers

contain data from first image

after PD . Note that an addi-

tional 75 frames for AGC (shutter)

stabilization may be required if

mouse movement occurred

while PD was high. (Refer to

Figure 12.)

Data valid time before the rising

of SCLK. (Refer to Figure 26.)

Pulse width to initiate the power

down cycle @ 1500 fps. (Refer

to Figure 12 and Figure 14.)

Pulse width to reset the serial

port @ 1500 fps (but may also

initiate a power down cycle.

Normal PD recovery sequence

to be followed. (Refer to

Figure 15.)

See Frame_Period register

section.

Refer to Figure 8.