XRT83L34 データシートの表示(PDF) - Exar Corporation

部品番号

コンポーネント説明

一致するリスト

XRT83L34 Datasheet PDF : 99 Pages

| |||

XRT83L34

xr

REV. 1.0.1 QUAD T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

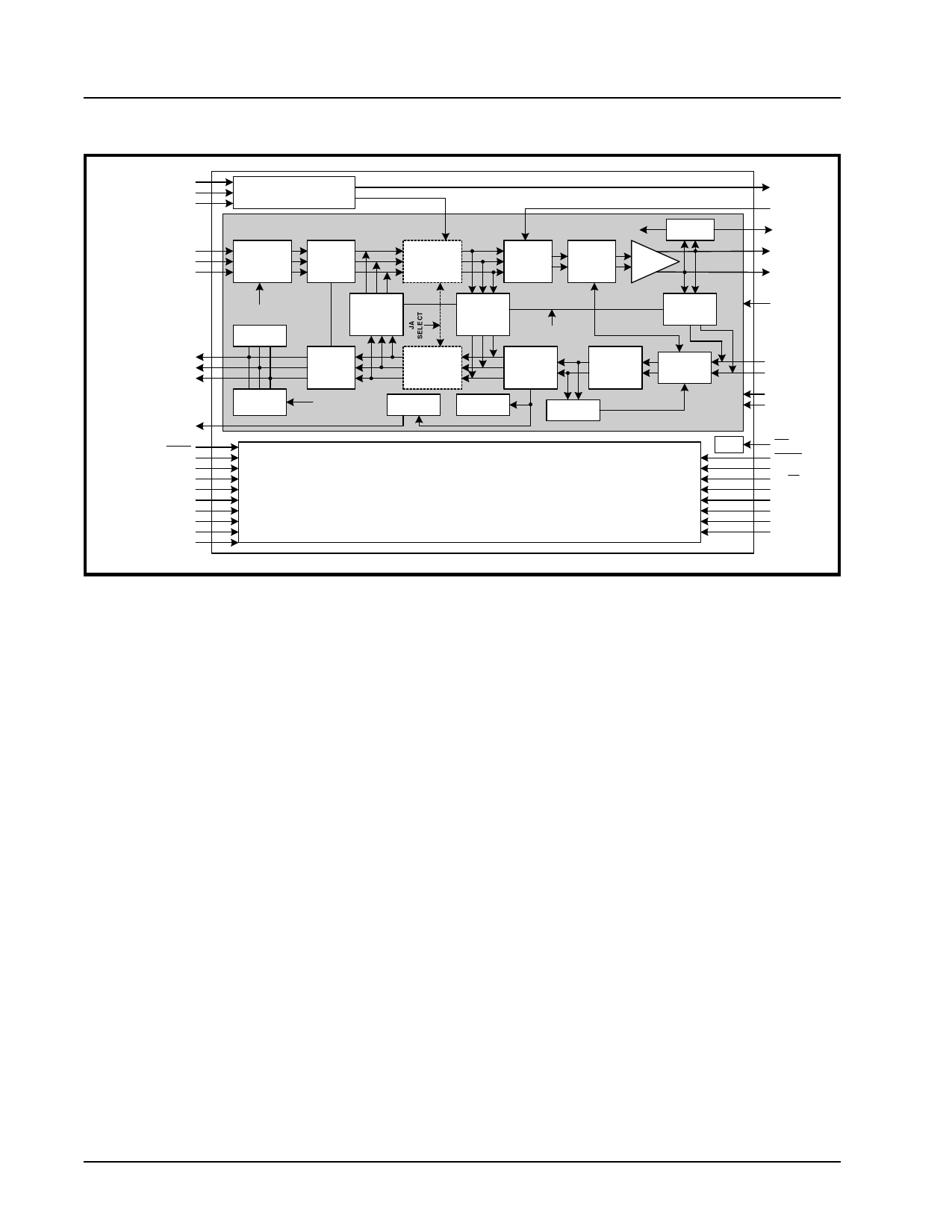

FIGURE 2. BLOCK DIAGRAM OF THE XRT83L34 T1/E1/J1 LIU (HARDWARE MODE)

MCLKE1

MCLKT1

CLKSEL[2:0]

TPOS_n/TDATA_n

TNEG_n/CODES_n

TCLK_n

RCLK_n

RNEG_n/LCV_n

RPOS_n/RDATA_n

RLOS_n

HW /HOST

GAUGE

JASEL1

JASEL0

RXTSEL

TXTSEL

TERSEL1

TERSEL0

RXRES1

RXRES0

MASTER CLOCK SYNTHESIZER

One of four Channels, CHANNEL_n - (n=0 : 3)

QRSS

PATTERN

GENERATOR

HDB3/

B8ZS

ENCODER

T X/RX JIT T ER

ATTENUATOR

T IM IN G

CONTROL

DFM

D R IV E

M O N IT O R

TX FILTER

& PULSE

SHAPER

L IN E

D R IV E R

QRSS ENABLE

QRSS

DETECTOR

NETWORK

LOOP

DETECTOR

REMOTE

LOOPBACK

D IG IT A L

LOOPBACK

LOOPBACK

ENABLE

HDB3/

B8ZS

DECODER

T X/RX JIT T ER

ATTENUATOR

TIMING &

DATA

RECOVERY

LBO[3:0]

PEAK

DETECTOR

& SLICER

NLCD ENABLE

LOS

DETECTOR

AIS

DETECTOR

E Q U A L IZ E R

CONTROL

LOCAL

ANALOG

LOOPBACK

RX

E Q U A L IZ E R

TEST

HARWARE CONTROL

MCLKOUT

TAOS_n

DMO_n

T T IP _n

T R IN G _n

TXON_n

RTIP_n

RRING_n

LOOP1_n

LOOP0_n

ICT

RESET

T R A T IO

SR/DR

EQC[4:0]

TCLKE

RCLKE

RXMUTE

ATAOS

FEATURES

• Fully integrated four channel long-haul or short-haul transceivers for E1,T1 or J1 applications

• Adaptive Receive Equalizer for up to 36dB cable attenuation

• Programable Transmit Pulse Shaper for E1,T1 or J1 short-haul interfaces

• Five fixed transmit pulse settings for T1 short-haul applications plus a fully programmable waveform

generator for transmit output pulse shaping that can be used for both T1 and E1 modes.

• Transmit Line Build-Outs (LBO) for T1 long-haul application from 0dB to -22.5dB in three 7.5dB steps

• Selectable receiver sensitivity from 0 to 36dB cable loss for T1 @772kHz and 0 to 43dB for E1 @1024kHz

• Receive monitor mode handles 0 to 29dB resistive attenuation along with 0 to 6dB of cable attenuation for

E1 and 0 to 3dB of cable attenuation for T1 modes

• Supports 75Ω and 120Ω (E1), 100Ω (T1) and 110Ω (J1) applications

• Internal and/or external impedance matching for 75Ω, 100Ω, 110Ω and 120Ω

• Tri-State transmit output and receive input capability for redundancy applications

• Provides High Impedance for Tx and Rx during power off

• Transmit return loss meets or exceeds ETSI 300-166 standard

• On-chip digital clock recovery circuit for high input jitter tolerance

• Crystal-less digital jitter attenuator with 32-bit or 64-bit FIFO selectable either in transmit or receive path

• On-chip frequency multiplier generates T1 or E1 Master clocks from variety of external clock sources

• High receiver interference immunity

• On-chip transmit short-circuit protection and limiting, and driver fail monitor output (DMO)

• Receive loss of signal (RLOS) output

• On-chip HDB3/B8ZS/AMI encoder/decoder functions

• QRSS pattern generator and detection for testing and monitoring

2