TSL25717 データシートの表示(PDF) - TEXAS ADVANCED OPTOELECTRONIC SOLUTIONS

部品番号

コンポーネント説明

一致するリスト

TSL25717 Datasheet PDF : 24 Pages

| |||

TSL2571

LIGHT-TO-DIGITAL CONVERTER

TAOS117A − FEBRUARY 2011

Wait Characteristics, VDD = 3 V, TA = 255C, WEN = 1 (unless otherwise noted)

PARAMETER

TEST CONDITIONS

CHANNEL

MIN TYP

Wait step size

WTIME = 0xFF

2.58 2.72

Wait number of integration steps

1

MAX

2.9

256

UNIT

ms

steps

AC Electrical Characteristics, VDD = 3 V, TA = 255C (unless otherwise noted)

PARAMETER†

TEST CONDITIONS

MIN

f(SCL)

Clock frequency (I2C only)

0

t(BUF)

Bus free time between start and stop condition

1.3

Hold time after (repeated) start condition. After

t(HDSTA)

this period, the first clock is generated.

0.6

t(SUSTA)

Repeated start condition setup time

0.6

t(SUSTO)

Stop condition setup time

0.6

t(HDDAT)

Data hold time

0

t(SUDAT)

Data setup time

100

t(LOW)

SCL clock low period

1.3

t(HIGH)

SCL clock high period

0.6

tF

Clock/data fall time

tR

Clock/data rise time

Ci

Input pin capacitance

† Specified by design and characterization; not production tested.

TYP MAX UNIT

400 kHz

μs

μs

μs

μs

μs

ns

μs

μs

300 ns

300 ns

10 pF

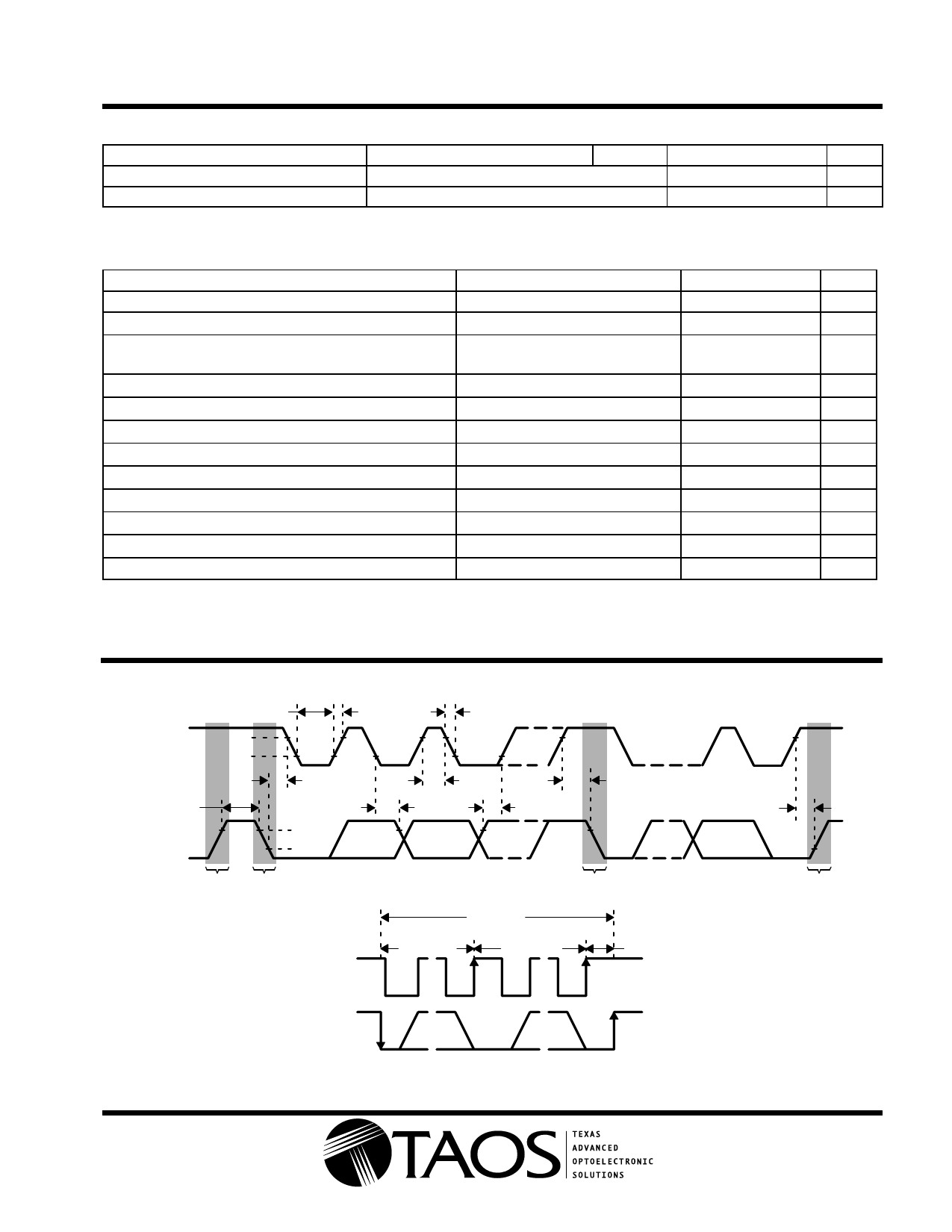

PARAMETER MEASUREMENT INFORMATION

SCL

t(BUF)

SDA

t(LOW)

t(R)

VIH

VIL

t(HDSTA)

t(HDDAT)

VIH

VIL

t(F)

t(HIGH) t(SUSTA)

t(SUDAT)

P

Stop

Condition

S

Start

Condition

SCL

S

Start

Stop

t(LOWSEXT)

SCLACK

SCLACK

t(LOWMEXT)

t(LOWMEXT)

t(LOWMEXT)

SDA

Figure 1. Timing Diagrams

The LUMENOLOGY r Company

r

r

www.taosinc.com

t(SUSTO)

P

Copyright E 2011, TAOS Inc.

5