IS61SP6436 データシートの表示(PDF) - Integrated Silicon Solution

部品番号

コンポーネント説明

一致するリスト

IS61SP6436 Datasheet PDF : 16 Pages

| |||

IS61SP6436

ISSI®

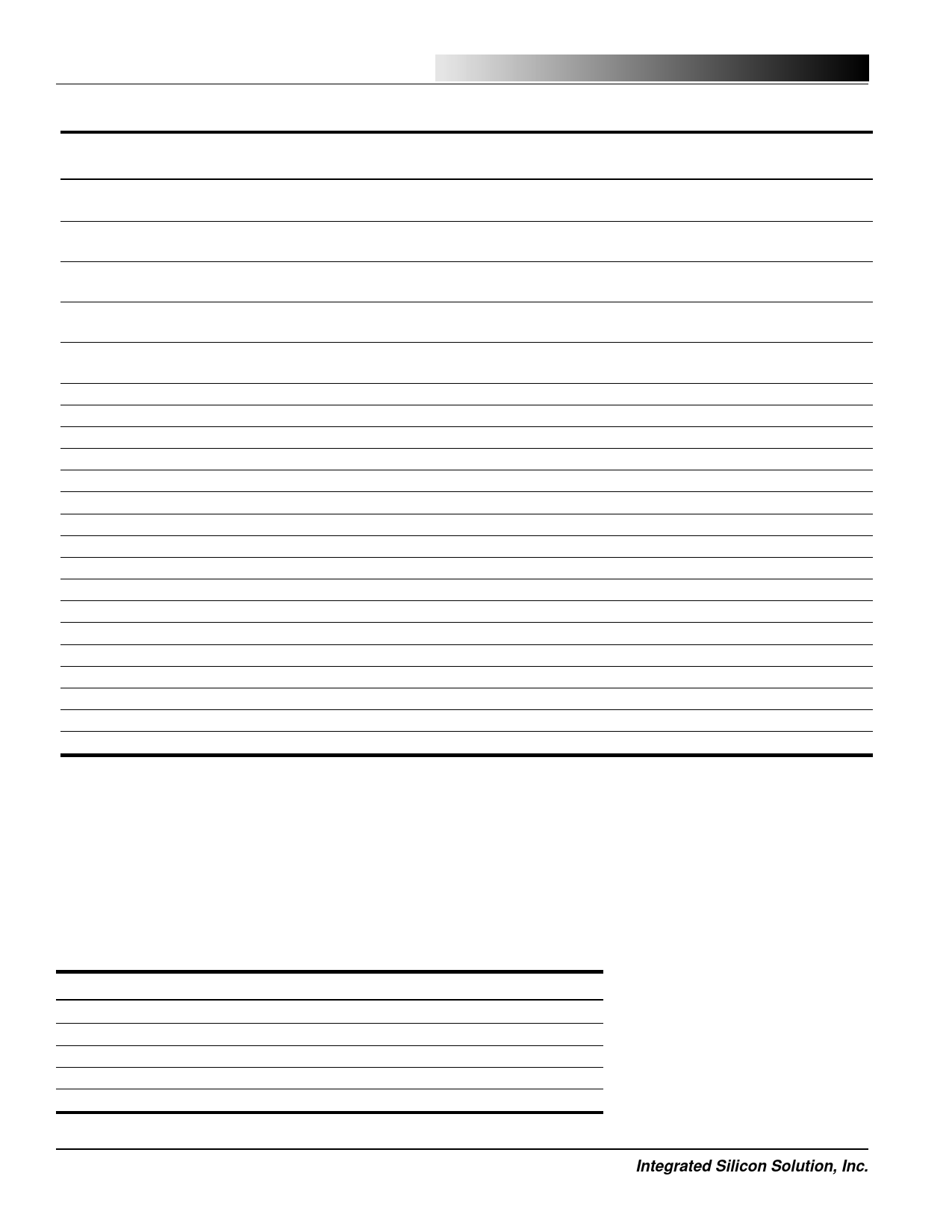

TRUTH TABLE

Operation

Deselected, Power-down

Address

Used CE CE2 CE2 ADSP ADSC ADV WRITE OE DQ

None

H

X

X

X

L

X

X

X High-Z

Deselected, Power-down

None

L

X

L

L

X

X

X

X High-Z

Deselected, Power-down

None

L

H

X

L

X

X

X

X High-Z

Deselected, Power-down

None

L

X

L

H

L

X

X

X High-Z

Deselected, Power-down

None

L

H

X

H

L

X

X

X High-Z

Read Cycle, Begin Burst

External

L

L

H

L

X

X

X

L

Q

Read Cycle, Begin Burst

External

L

L

H

L

X

X

X

H High-Z

Write Cycle, Begin Burst

External

L

L

H

H

L

X

L

X

D

Read Cycle, Begin Burst

External

L

L

H

H

L

X

H

L

Q

Read Cycle, Begin Burst

External

L

L

H

H

L

X

H

H High-Z

Read Cycle, Continue Burst

Read Cycle, Continue Burst

Read Cycle, Continue Burst

Read Cycle, Continue Burst

Next

Next

Next

Next

XX

X

H

H

L

H

L

Q

XX

X

H

H

L

H

H High-Z

HX

X

X

H

L

H

L

Q

HX

X

X

H

L

H

H High-Z

Write Cycle, Continue Burst Next

XX

X

H

H

L

L

X

D

Write Cycle, Continue Burst Next

HX

X

X

H

L

L

X

D

Read Cycle, Suspend Burst Current

XX

X

H

H

H

H

L

Q

Read Cycle, Suspend Burst Current

XX

X

H

H

H

H

H High-Z

Read Cycle, Suspend Burst Current

HX

X

X

H

H

H

L

Q

Read Cycle, Suspend Burst Current

Write Cycle, Suspend Burst Current

HX

X

X

H

H

H

H High-Z

XX

X

H

H

H

L

X

D

Write Cycle, Suspend Burst Current

HX

X

X

H

H

L

X

D

Notes:

1. All inputs except OE must meet setup and hold times for the Low-to-High transition of clock (CLK).

2. Wait states are inserted by suspending burst.

3. X means don't care. WRITE=L means any one or more byte write enable signals (BW1-BW4) and BWE are LOW or GW is LOW.

WRITE=H means all byte write enable signals are HIGH.

4. For a Write operation following a Read operation, OE must be HIGH before the input data required setup time and held HIGH

throughout the input data hold time.

5. ADSP LOW always initiates an internal READ at the Low-to-High edge of clock. A WRITE is performed by setting one or more

byte write enable signals and BWE LOW or GW LOW for the subsequent L-H edge of clock.

PARTIAL TRUTH TABLE

Function

GW BWE BW1 BW2 BW3 BW4

READ

READ

WRITE Byte 1

WRITE All Bytes

WRITE All Bytes

H

H

X

X

XX

H

L

H

H

HH

H

L

L

H

HH

H

L

L

L

LL

L

X

X

X

XX

4

Integrated Silicon Solution, Inc.

SR029-1C

08/11/99