MSM7620 データシートの表示(PDF) - Oki Electric Industry

部品番号

コンポーネント説明

一致するリスト

MSM7620 Datasheet PDF : 28 Pages

| |||

¡ Semiconductor

MSM7620

(2/5)

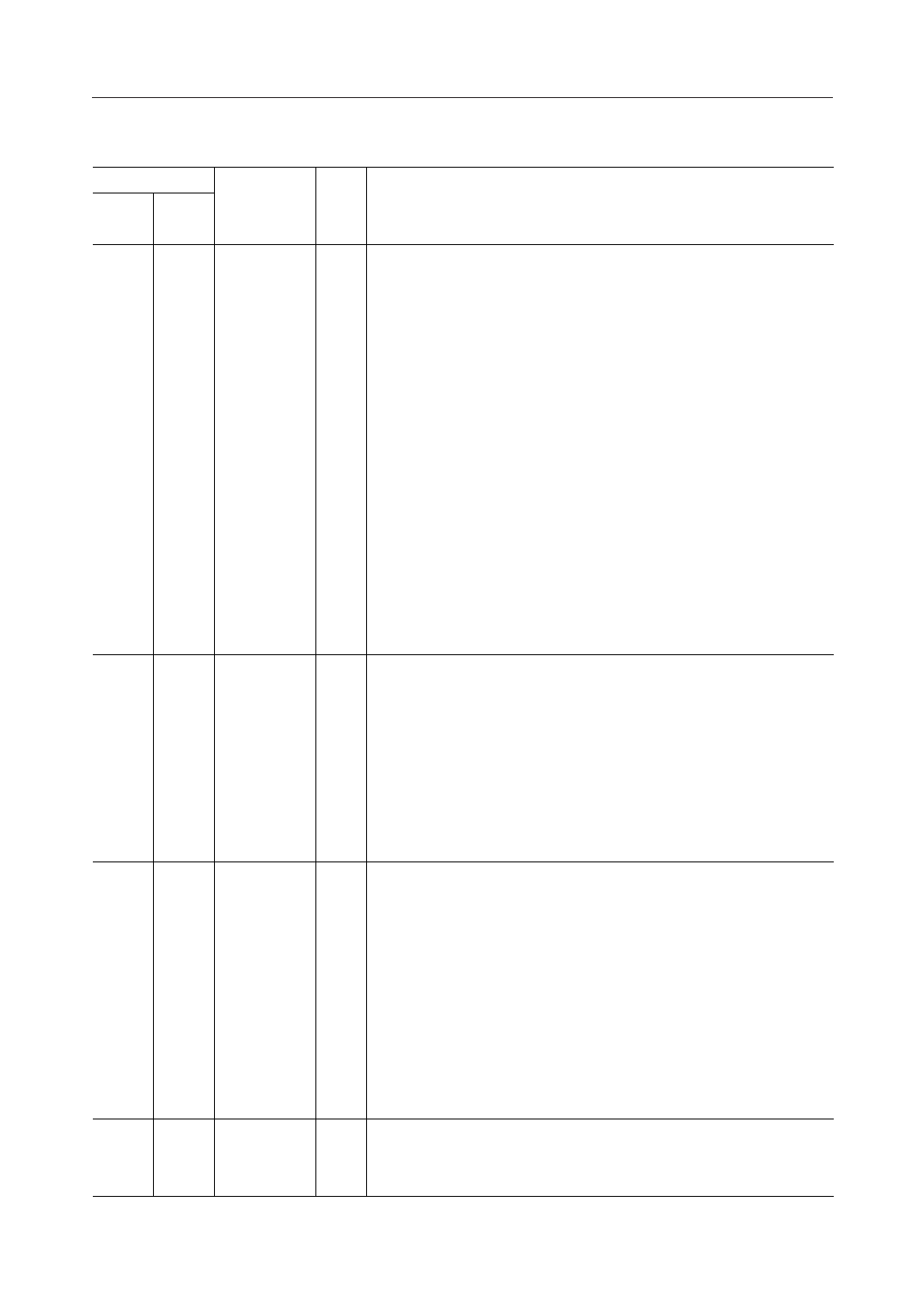

Pin

32-pin 64-pin

SSOP QFP

6

5

7

6

8

8

9

10

Symbol

ATT

INT

IRLD

SIN

Type

Description

I Control for the ATT function that prevents howling by attenuators (ATT)

for the RIN input and SOUT output.

If there is input only to RIN, then the ATT for the SOUT output is

activated.

If there is no input to SIN, or if there is input to both SIN and RIN, the

ATT for the RIN input is activated.

Either the ATT for the RIN output or the ATT for the SOUT is always

activated in all cases, and the attenuation of ATT is 6 dB.

• Single Chip or Master Chip in a Cascade Connection

"H": ATT OFF

"L": ATT ON

"L" is recommended for echo cancellation.

• Slave Chip in a Cascade Connection

• Fixed at "L"

This input signal is loaded in synchronization with the falling edge of the

INT signal or the rising edge of the RST signal.

I Interrupt signal which starts 1 cycle (8 kHz) of the signal processing.

Signal processing starts when H-to-L transition is detected.

• Single Chip or Master Chip in a Cascade Connection

Connect the IRLD pin.

• Slave Chip in a Cascade Connection

Connect the IRLD pin of the master chip.

INT input is invalid for 100 ms after reset due to initialization. Refer to

the control pin connection example.

O Load detection signal when the SIN and RIN serial input data is loaded

in the internal registers.

• Single Chip

Connect to the INT pin.

• Master Chip in a Cascade Connection

Connect to the INT pin of the master chip and all the slave

chips.

• Slave Chip in a Cascade Connection

Leave open.

Refer to the control pin connection example.

I Transmit serial data.

Input the m-law PCM signal synchronized to SYNC and SCK. Data is

read in at the fall of SCK.

6/28