MB88155-100 データシートの表示(PDF) - Fujitsu

部品番号

コンポーネント説明

一致するリスト

MB88155-100 Datasheet PDF : 24 Pages

| |||

MB88155

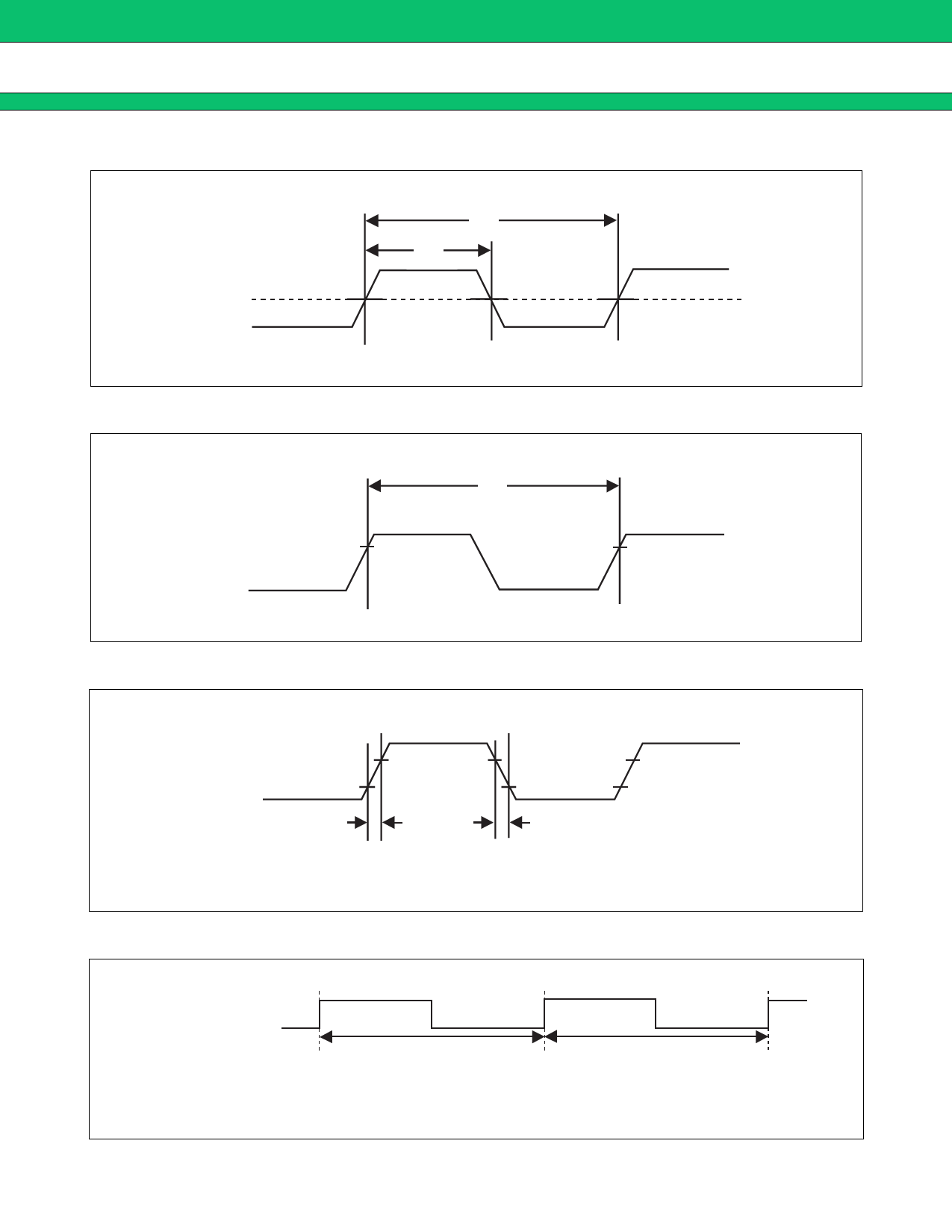

■ OUTPUT CLOCK DUTY CYCLE (tDCC, tDCR = tb/ta)

ta

tb

CKOUT,

REFOUT

■ INPUT FREQUENCY (fin = 1/tin)

tin

XIN

1.5 V

0.8 VDD

■ OUTPUT SLEW RATE (SRC, SRR)

CKOUT,

REFOUT

tr

tf

Note : SRC = (2.4 − 0.4) /tr, SRC = (2.4 − 0.4) /tf

SRR = (2.4 − 0.4) /tr, SRR = (2.4 − 0.4) /tf

■ CYCLE-CYCLE JITTER (tJC = |tn − tn + 1| )

2.4 V

0.4 V

CKOUT

tn

tn+1

Note : Cycle-cycle jitter indicates the difference between a certain cycle and the immediately

succeeding (or preceding) cycle.

14