L6382D データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

一致するリスト

L6382D Datasheet PDF : 21 Pages

| |||

L6382D

Pin settings

Name

9

10

11

12

13

14

15

16

17

18

19

20

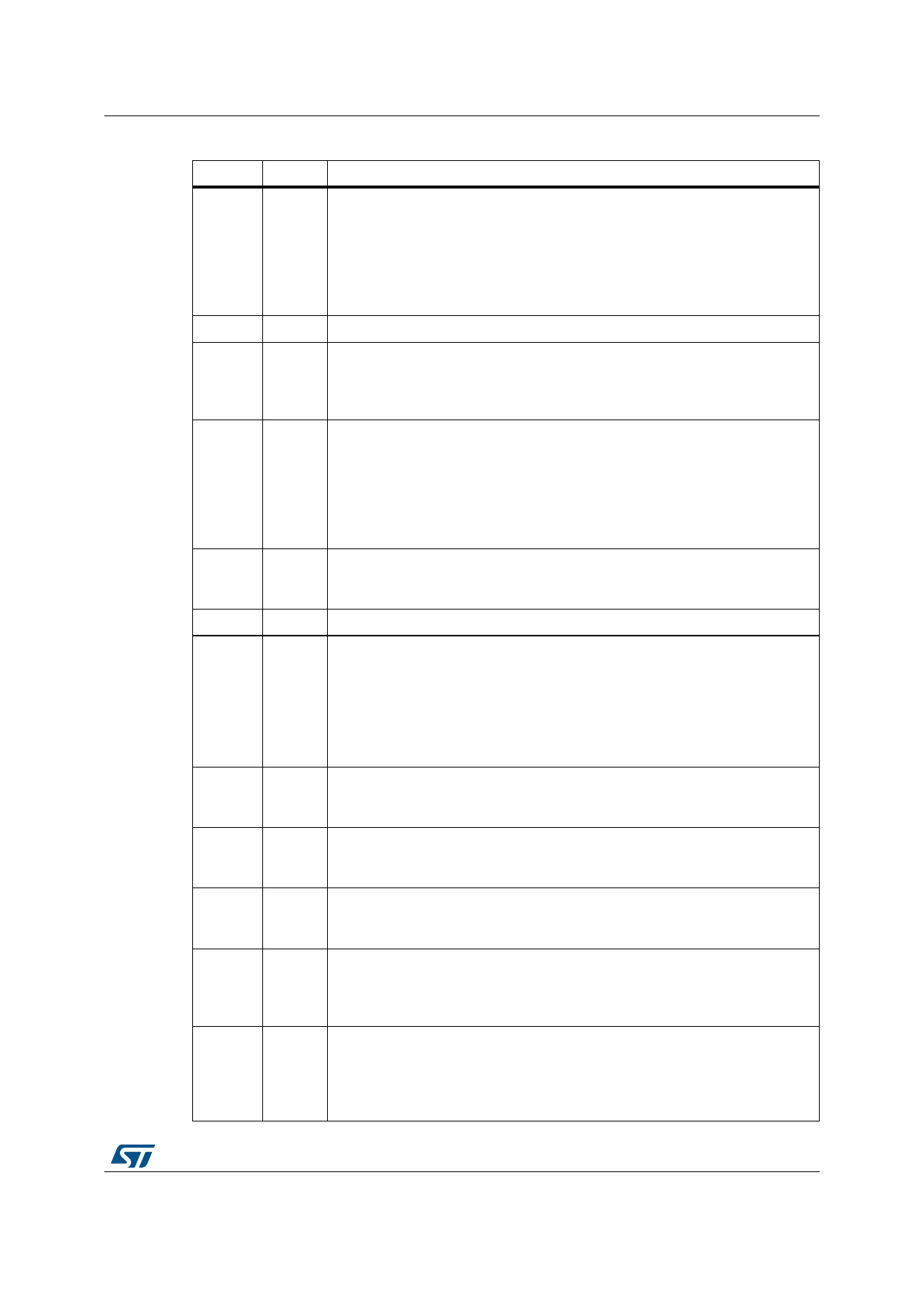

Table 1. Pin description (continued)

Pin no.

Description

LSG

Low-side driver output. This pin must be connected to the gate of the half-

bridge low-side power MOSFET. A resistor connected between this pin and the

power MOS gate can be used to reduce the peak current.

An internal 20 k resistor toward ground avoids spurious and undesired

MOSFET turn-on.

The totem pole output stage is able to drive power with a peak current of 120

mA source and 120 mA sink.

Vcc Supply voltage for the signal part of the IC and for the drivers.

BOOT

High-side gate drive floating supply voltage. The bootstrap capacitor

connected between this pin and pin 13 (OUT) is fed by an internal

synchronous bootstrap diode driven in phase with the low-side gate drive. This

patented structure normally replaces the external diode.

HSG

High-side driver output. This pin must be connected to the gate of the half

bridge high-side power MOSFET. A resistor connected between this pin and

the power MOS gate can be used to reduce the peak current.

An internal 20 k resistor toward OUT pin avoids spurious and undesired

MOSFET turn-on

The totem pole output stage is able to drive the power MOS with a peak

current of 120 mA source and 120 mA sink.

OUT

High-side gate drive floating ground. Current return for the high-side gate drive

current. Layout carefully the connection of this pin to avoid too large spikes

below ground.

N.C. Not connected.

HVSU

High voltage startup. The current flowing into this pin charges the capacitor

connected between pin Vcc and GND to start up the IC. While the chip is in

save mode, the generator is cycled on-off between turn-on and save mode

voltages. When the chip works in operating mode the generator is shut down

and it is re-enabled when the Vcc voltage falls below the UVLO threshold.

According to the required VREF pin current, this pin can be connected to the

rectified mains voltage either directly or through a resistor.

N.C.

High voltage spacer. The pin is not connected internally to isolate the high

voltage pin and comply with safety regulations (creepage distance) on the

PCB.

HEG

Output for the HEI block; this driver can be used to drive the MOS. An internal

20 k resistor toward ground avoids spurious and undesired MOSFET turn-

on.

CSO

Output of current sense comparator, compatible with TTL logic signal; during

operating mode, the pin is forced low whereas whenever the OC comparator is

triggered (CSI > 0.5 V typ.) the pin latches high.

Input of current sense comparator, it is enabled only during operating mode;

CSI

when the pin voltage exceeds the internal threshold, the CSO pin is forced

high and the half bridge drivers are disabled. It exits from this condition by

either cycling the Vcc below the UVLO or with LGI = HGI = low simultaneously.

VREF

Voltage reference. During normal mode an internal generator provides an

accurate voltage reference that can be used to supply up to 30 mA (during

operating mode) to an external circuit. A small film capacitor (0.22 F min.),

connected between this pin and GND is recommended to ensure the stability

of the generator and to prevent noise from affecting the reference.

DocID10972 Rev 8

5/21

21