IDT7028L15PF データシートの表示(PDF) - Integrated Device Technology

部品番号

コンポーネント説明

一致するリスト

IDT7028L15PF Datasheet PDF : 17 Pages

| |||

IDT7028L

High-Speed 64K x 16 Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

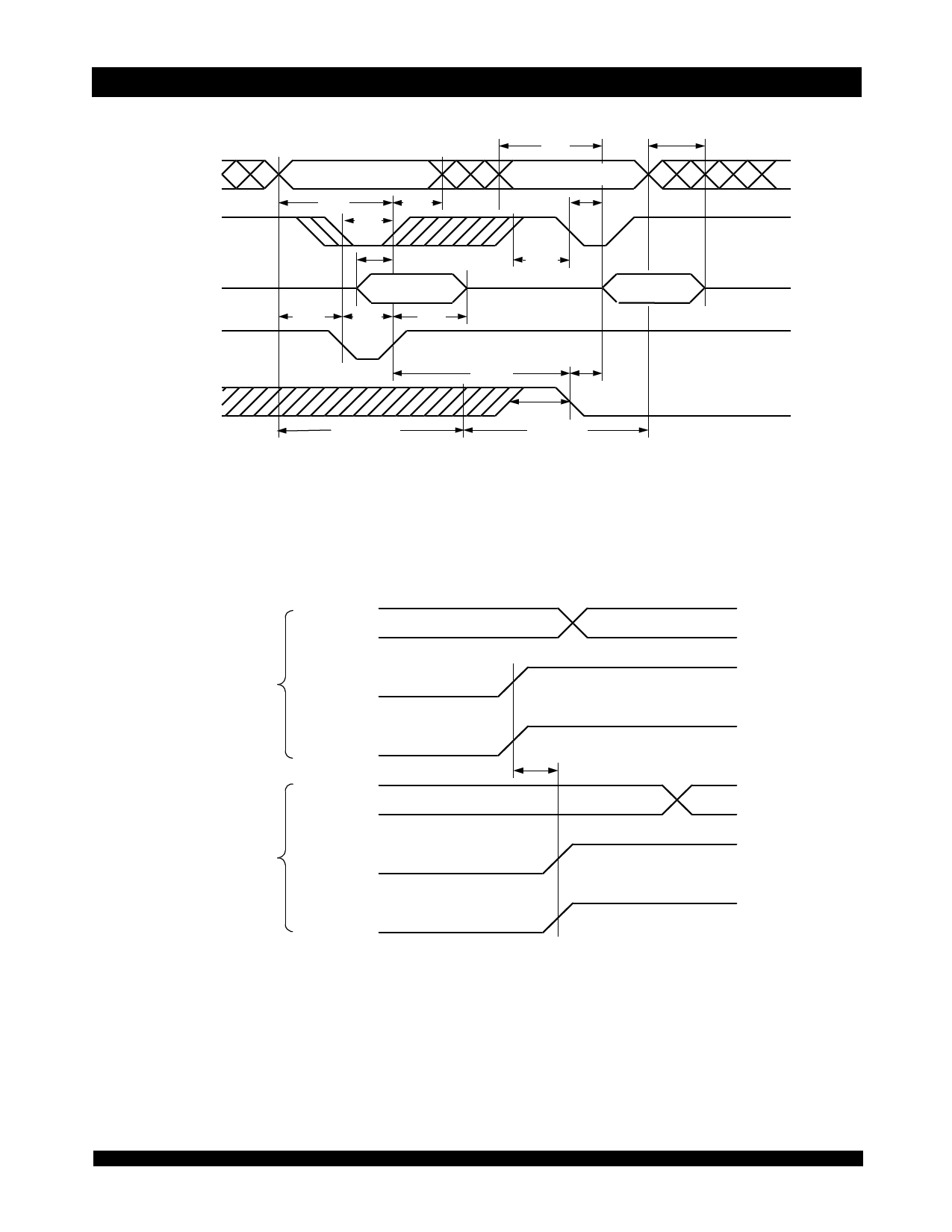

Timing Waveform of Semaphore Read after Write Timing, Either Side(1)

A0-A2

SEM

DATA0

R/W

VALID ADDRESS

tAW

tWR

tEW

tDW

DATAIN VALID

tAS

tWP

tDH

tSAA

tOH

VALID ADDRESS

tACE

tSOP

DATAOUT

VALID(2)

tSWRD

tAOE

OE

tSOP

Write Cycle

Read Cycle

NOTES:

1. CE = VIH or UB and LB = VIH for the duration of the above timing (both write and read cycle) (Refer to Chip Enable Truth Table).

2. "DATAOUT VALID" represents all I/O's (I/O0 - I/O15) equal to the semaphore value.

4836 drw 09

Timing Waveform of Semaphore Write Contention(1,3,4)

A0"A"-A2"A"

MATCH

SIDE(2) "A"

R/W"A"

SEM"A"

A0"B"-A2"B"

tSPS

MATCH

SIDE(2) "B"

R/W"B"

SEM"B"

4836 drw 10

NOTES:

1. DOR = DOL = VIL, CEL = CER = VIH or both UB and LB = VIH (Refer to Chip Enable Truth Table).

2. All timing is the same for left and right ports. Port "A" may be either left or right port. "B" is the opposite from port "A".

3. This parameter is measured from R/W"A" or SEM"A" going HIGH to R/W"B" or SEM"B" going HIGH.

4. If tSPS is not satisfied, the semaphore will fall positively to one side or the other, but there is no guarantee which side will obtain the flag.

6.942