HSP45116GM-15883 データシートの表示(PDF) - Intersil

部品番号

コンポーネント説明

一致するリスト

HSP45116GM-15883 Datasheet PDF : 18 Pages

| |||

HSP45116

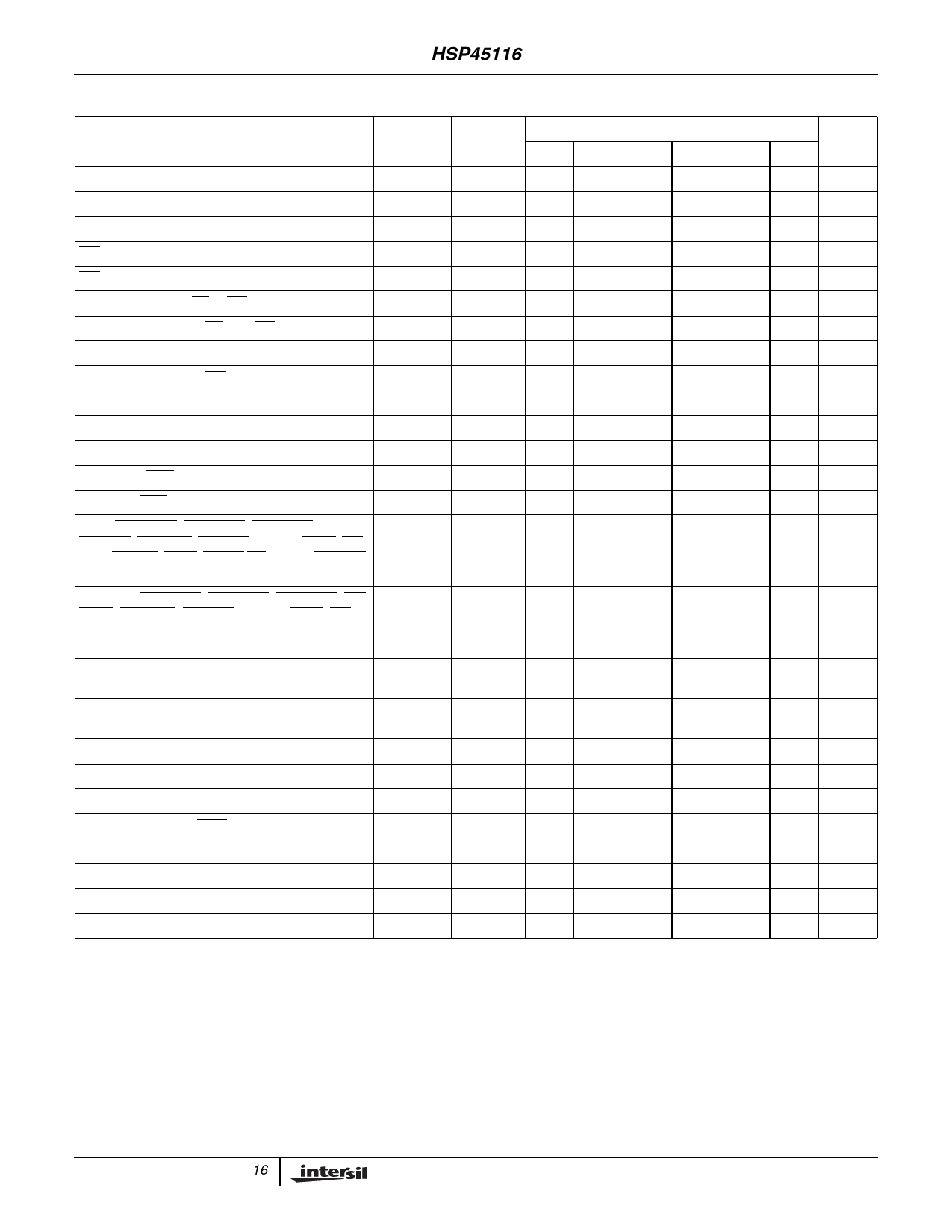

AC Electrical Specifications VCC = 5.0V ±5%, TA = 0oC to 70oC (Note 5)

-15 (15MHz) -25 (25.6MHz) -33 (33MHz)

PARAMETER

SYMBOL NOTES MIN MAX MIN MAX MIN MAX UNITS

CLK Period

CLK High

CLK Low

WR Low

WR High

Setup Time; AD0-1, CS to WR Going High

Hold Time; AD0, AD1, CS from WR Going High

Setup Time C0-15 from WR Going High

Hold Time C0-15 from WR Going High

Setup time WR High to CLK High

Setup Time MOD0-1 to CLK Going High

Hold Time MOD0-1 from CLK Going High

Setup Time PACI to CLK Going High

Hold Time PACI from CLK Going High

Setup ENPHREG, ENCFREG, ENOFREG,

ENPHAC, ENTIREG, CLROFR, PMSEL, LOAD, ENI,

ACC, BINFMT, PEAK, MODPI/2PI, SH0-1, RBYTILD

from CLK Going High

tCP

tCH

tCL

tWL

tWH

tAWS

tAWH

tCWS

tCWH

tWC

tMCS

tMCH

tPCS

tPCH

tECS

66

-

39

-

30

-

ns

26

-

15

-

12

-

ns

26

-

15

-

12

-

ns

26

-

15

-

12

-

ns

26

-

15

-

12

-

ns

18

-

13

-

13

-

ns

0

-

0

-

0

-

ns

20

-

15

-

15

-

ns

0

-

0

-

0

-

ns

7

20

-

16

-

12

-

ns

20

-

15

-

15

-

ns

0

-

0

-

0

-

ns

25

-

15

-

11

-

ns

0

-

0

-

0

-

ns

18

-

12

-

12

-

ns

Hold Time ENPHREG, ENCFREG, ENOFREG, EN-

PHAC, ENTIREG, CLROFR, PMSEL, LOAD, ENI,

ACC, BINFMT, PEAK, MODPI/2PI, SH0-1, RBYTILD

from CLK Going High

tECH

0

-

0

-

0

-

ns

Setup Time RIN0-18, IMIN0-18 to CLK

tDS

Going High

18

-

12

-

12

-

ns

Hold Time RIN0-18, IMIN0-18 from CLK

tDH

Going High

0

-

0

-

0

-

ns

CLK to Output Delay RO0-19, IO0-19

tDO

-

40

-

24

-

19

ns

CLK to Output Delay DET0-1

tDEO

-

40

-

27

-

20

ns

CLK to Output Delay PACO

tPO

-

30

-

20

-

12

ns

CLK to Output Delay TICO

tTO

-

30

-

20

-

12

ns

Output Enable Time OER, OEI, OEREXT, OEIEXT

tOE

-

25

-

20

-

20

ns

OUTMUX0-1 to Output Delay

tMD

-

40

-

28

-

26

ns

Output Disable Time

tOD

6

-

20

-

15

-

15

ns

Output Rise, Fall Time

tRF

6

-

8

-

8

-

6

ns

NOTES:

5. AC testing is performed as follows: Input levels (CLK Input) 4.0V and 0V; input levels (all other inputs) 0V and 3.0V; timing reference levels (CLK)

2.0V; all others 1.5V. Output load per test load circuit with switch closed and CL = 40pF. Output transition is measured at VOH ≥ 1.5V and VOL

≤ 1.5V.

6. Controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or design

changes.

7. Applicable only when outputs are being monitored and ENCFREG, ENPHREG, or ENTIREG is active.

16