HFA3863 データシートの表示(PDF) - Intersil

部品番号

コンポーネント説明

一致するリスト

HFA3863 Datasheet PDF : 39 Pages

| |||

HFA3863

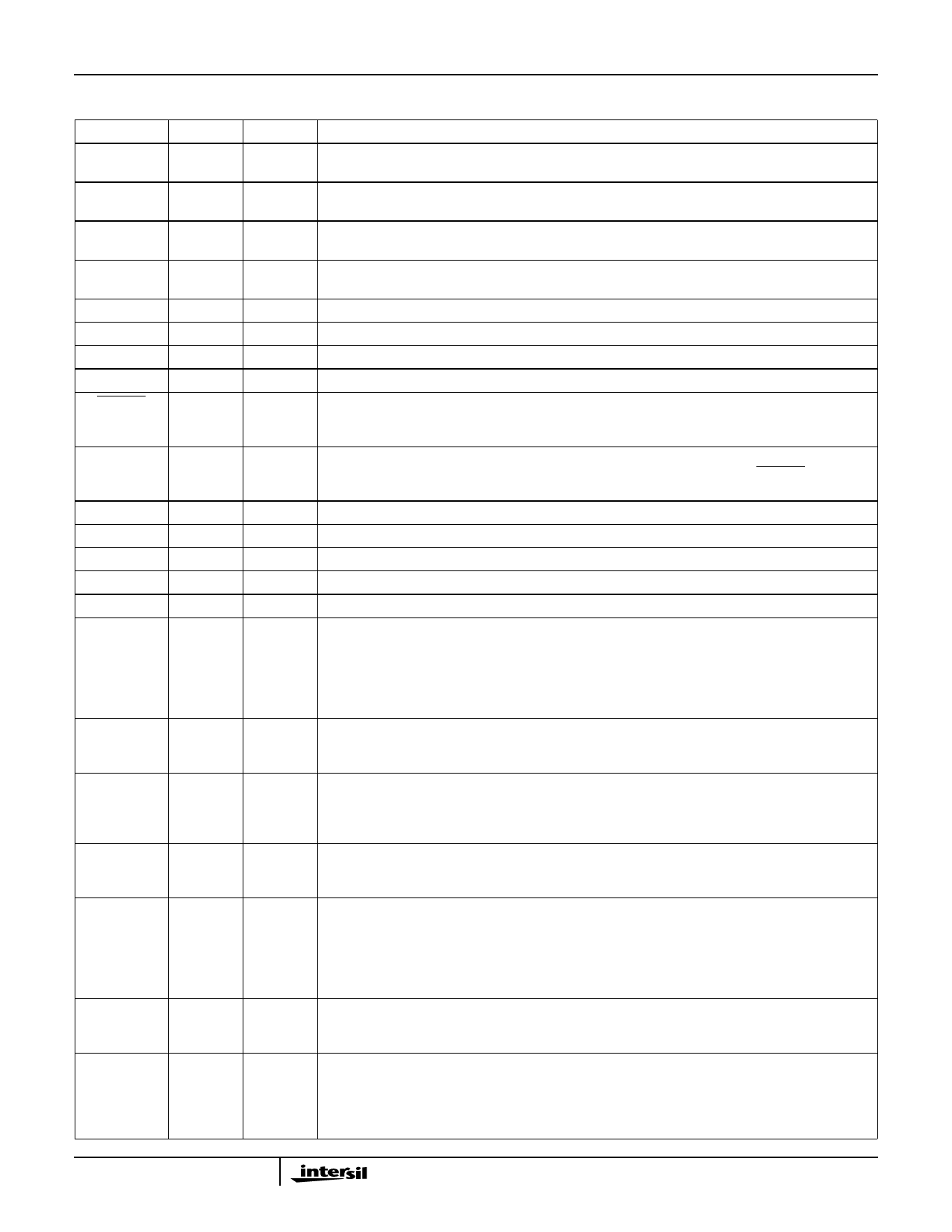

Pin Descriptions

NAME

PIN

VDDA (Analog) 12, 17, 22,

31

VDDD (Digital) 2, 8, 37, 41,

57

GNDa

(Analog)

9, 15, 20,

25, 28

GNDd (Digital) 1, 7, 36, 43,

56

TYPE I/O

Power

Power

Ground

Ground

DESCRIPTION

DC power supply 2.7V - 3.6V (Not Hard wired Together On Chip).

DC power supply 2.7 - 3.6V.

DC power supply 2.7 - 3.6V, ground (not hard wired together on chip).

DC power supply 2.7 - 3.6V, ground.

VREF

IREF

RXI, ±

RXQ, ±

ANTSEL

16

21

10/11

13/14

39

I

Voltage reference for A/D’s and D/A’s.

I

Current reference for internal ADC and DAC devices. Requires a 12kΩ resistor to ground.

I

Analog input to the internal 6-bit A/D of the In-phase received data. Balanced differential 10+/11-.

I

Analog input to the internal 6-bit A/D of the Quadrature received data. Balanced differential 13+/14-.

O

The antenna select signal changes state as the receiver switches from antenna to antenna during the

acquisition process in the antenna diversity mode. This is a complement for ANTSEL (pin 40) for

differential drive of antenna switches.

ANTSEL

40

RX_IF_DET

19

O

The antenna select signal changes state as the receiver switches from antenna to antenna during the

acquisition process in the antenna diversity mode. This is a complement for ANTSEL (pin 39) for

differential drive of antenna switches.

I

Analog input to the receive power A/D converter for AGC control.

RX_IF_AGC

34

RX_RF_AGC

38

TX_AGC_IN

18

O

Analog drive to the IF AGC control.

O

Drive to the RF AGC stage attenuator. CMOS digital.

I

Input to the transmit power A/D converter for transmit AGC control.

TX_IF_AGC

35

TX_PE

62

O

Analog drive to the transmit IF power control.

I

When active, the transmitter is configured to be operational, otherwise the transmitter is in standby

mode. TX_PE is an input from the external Media Access Controller (MAC) or network processor to

the HFA3863. The rising edge of TX_PE will start the internal transmit state machine and the falling

edge will initiate shutdown of the state machine. TX_PE envelopes the transmit data except for the

last bit. The transmitter will continue to run for 4µs after TX_PE goes inactive to allow the PA to

shutdown gracefully.

TXD

58

TXCLK

55

TX_RDY

59

CCA

60

I

TXD is an input, used to transfer MAC Payload Data Unit (MPDU) data from the MAC or network

processor to the HFA3863. The data is received serially with the LSB first. The data is clocked in the

HFA3863 at the rising edge of TXCLK.

O

TXCLK is a clock output used to receive the data on the TXD from the MAC or network processor to

the HFA3863, synchronously. Transmit data on the TXD bus is clocked into the HFA3863 on the rising

edge. The clocking edge is also programmable to be on either phase of the clock. The rate of the clock

will be dependent upon the data rate that is programmed in the signalling field of the header.

O

TX_RDY is an output to the external network processor indicating that Preamble and Header

information has been generated and that the HFA3863 is ready to receive the data packet from the

network processor over the TXD serial bus.

O

Clear Channel Assessment (CCA) is an output used to signal that the channel is clear to transmit. The

CCA may be configured to one of four possible algorithms. The CCA algorithm and its features are

described elsewhere in the data sheet.

Logic 0 = Channel is clear to transmit.

Logic 1 = Channel is NOT clear to transmit (busy).

This polarity is programmable and can be inverted.

RXD

53

RXCLK

52

O

RXD is an output to the external network processor transferring demodulated Header information and

data in a serial format. The data is sent serially with the LSB first. The data is frame aligned with

MD_RDY.

O

RXCLK is the bit clock output. This clock is used to transfer Header information and payload data

through the RXD serial bus to the network processor. This clock reflects the bit rate in use. RXCLK is

held to a logic “0” state during the CRC16 reception. RXCLK becomes active after the SFD has been

detected. Data should be sampled on the rising edge. This polarity is programmable and can be

inverted.

4-3