HFA3842A データシートの表示(PDF) - Intersil

部品番号

コンポーネント説明

一致するリスト

HFA3842A Datasheet PDF : 27 Pages

| |||

HFA3842A

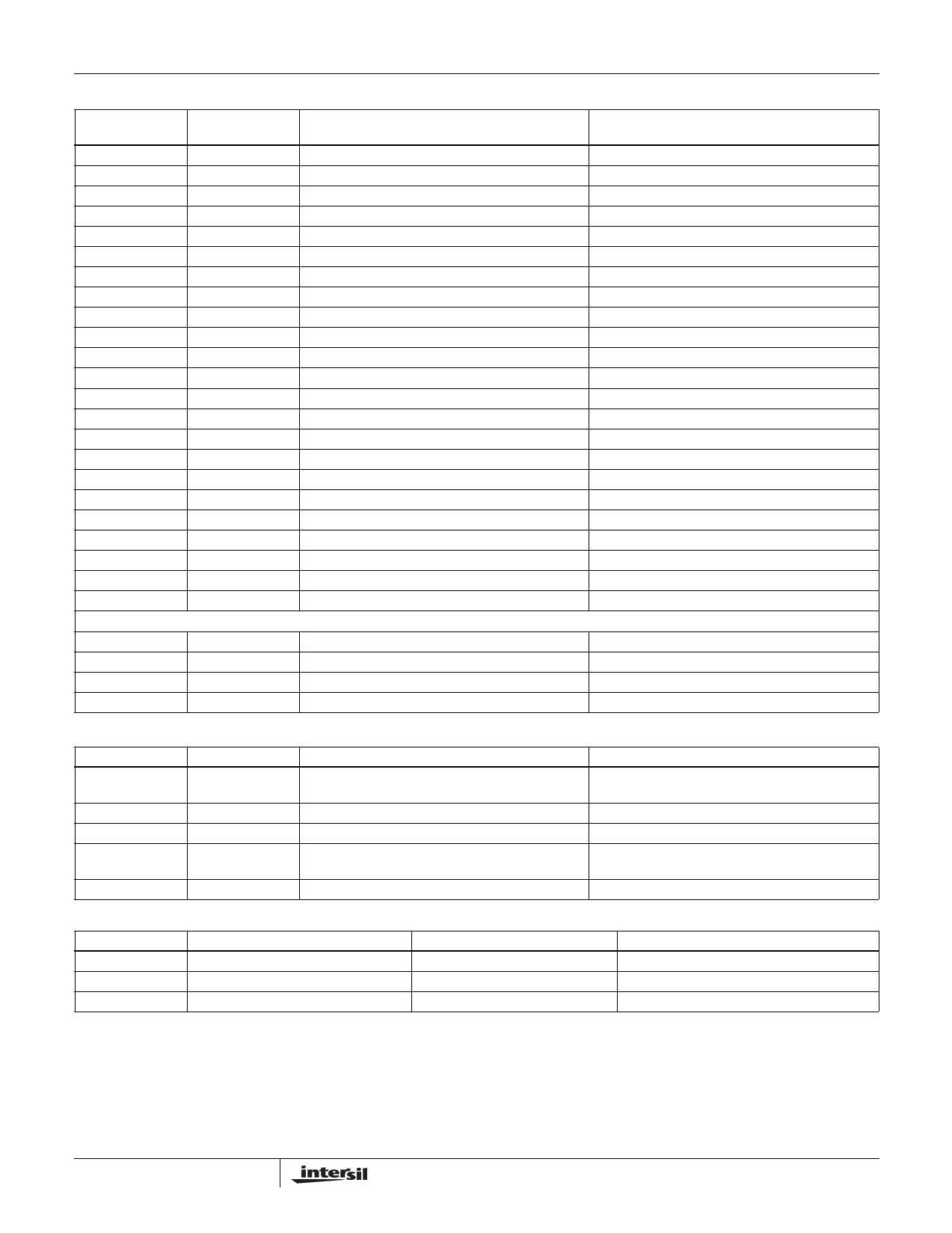

TABLE 2. GENERAL PURPOSE AND EEPROM PORT PINS (Continued)

PIN NAME

PIN NUMBER

PIN I/O TYPE

DESCRIPTION OF FUNCTION

(IF OTHER THAN IO PORT)

PJ0

31

CMOS BiDir, 2mA, 50K Pull Down

MMI Clock (SCLK)

PJ1

32

CMOS BiDir, 2mA, 50K Pull Down

MMI Serial Data (SD)

PJ3

29

CMOS BiDir, 2mA

MMI Device Enable 0 (CS_BAR)

PJ4

65

CMOS BiDir, 2mA

MMI Device Enable 1 (PE1)

PJ5

8

CMOS BiDir, 2mA, 50K Pull Up

MBUS Request (LE_IF)

PJ6

7

CMOS BiDir, 2mA

MBUS Grant; LED

PJ7

9

CMOS BiDir, 2mA, 50K Pull Up

(RADIO_PE)

PK0

35

CMOS BiDir, 2mA, ST, 50K Pull Down

MPSI Clock (LE_RF)

PK1

34

CMOS BiDir, 2mA, 50K Pull Down

MPSI Data Out (SYNTHCLK)

PK2

33

CMOS BiDir, 2mA, 50K Pull Down

MPSI Data In (SYNTHDATA)

PK3

63

CMOS BiDir, 2mA

PK4

64

CMOS BiDir, 2mA

MPSI Device Select 0 (PA_PE)

MPSI Device Select 1 (PE2)

PK5

21

CMOS BiDir, 2mA

PHY Data Available (MDREADY)

PK6

22

CMOS BiDir, 2mA

PK7

23

CMOS BiDir, 2mA

PHY Medium Busy (CCA)

PHY Energy Detect (CAL_EN)

PL0

15

CMOS BiDir, 2mA

Transmitter Enable (TX_PE)

PL1

27

CMOS BiDir, 2mA

PL2

26

CMOS BiDir, 2mA

Receiver Enable (or PHY Sleep Control) (RX_PE)

PHY Reset (RESET_BB)

PL3

28

CMOS BiDir, 2mA

Antenna Select (T/R_SW_BAR)

PL4

43

CMOS BiDir, 2mA

MBUS Address Bit 19 (MA19)

PL5 (USB+)

12

CMOS BiDir, 2mA, (Also USB Transceiver)

MBUS Address Bit 20 (USB+)

PL6 (USB-)

11

CMOS BiDir, 2mA, (Also USB Transceiver)

MBUS Address Bit 21 (USB-)

PL7

93

SERIAL EEPROM PORT PINS

CMOS BiDir, 2mA, Pull Down

PHY Transmit Ready (T/R_SW)

PJ0

31

CMOS BiDir

SCLK, Serial Clock

PJ1

30

CMOS BiDir, 50K Pull Down

SD, Serial Data Out

PJ2

32

CMOS BiDir, 50K Pull Down

MISO, Serial Data IN

TCLKIN (CS_)

10

CMOS BiDir

CS_, Chip Select

PIN NAME

CLKIN

LFXTALI

LFXTALO

CLKOUT

TCLKIN

PIN NUMBER

40

TABLE 3. CLOCKS

PIN I/O TYPE

CMOS Input, ST Pull Down

39

Analog Input

41

CMOS Output, 2mA

38

CMOS, TS Output, 2mA

10

CMOS BiDir, 2mA, 50K Pull Down

DESCRIPTION

External Clock Input (at >= 2X Desired MCLK

Frequency, Typically 44-48MHz)

32.768kHz Crystal Input (Note 2)

32.768kHz Crystal Output

Clock Output (Selectable as MCLK, TCLK, or

TOUT0)

Alternate clock input for timers

TABLE 4. POWER

PIN NAME

PIN NUMBER

PIN I/O TYPE

DESCRIPTION

VCC

14, 25, 53, 66, 83, 98, 124

3.3V Supply

VCC_IO5

105

5V Tolerance Supply

VSS

13, 24, 37, 42, 52, 67, 82, 97, 115 GND

ST = Schmitt Trigger (Hysteresis), TS = Three-State. Signals ending with “-” are active low.

NOTE:

2. Pin 39 (VCC_CORE3 in 3841), has been reassigned as LFXTALI. For 3841 compatibility, it may be tied to VCC.

Pin 62 (TRST- in 3841) has been reassigned as MLBE. For 3841 compatibility, it may be tied low through 1K.

Pin 105 (VCC_IO5 in 3841) has been reassigned as USB ATTACHED. For 3841 compatibility, it may be tied to VCC.

Output pins typically drive to positive voltage rail less 0.1V. Hence with a supply of 2.7V the output will just meet 5V TTL signal levels at

rated loads.

4