HD74HC112FPEL データシートの表示(PDF) - Renesas Electronics

部品番号

コンポーネント説明

一致するリスト

HD74HC112FPEL Datasheet PDF : 7 Pages

| |||

HD74HC112

Dual J-K Flip-Flops (with Preset and Clear)

REJ03D0562-0200

(Previous ADE-205-435)

Rev.2.00

Oct 11, 2005

Description

Each flip-flop has independent J, K, preset, clear and clock inputs and Q and Q outputs. This device is edge sensitive to

the clock input and change state on the negative going transition of the clock pulse. Clear and preset are independent of

the clock and accomplished by a low logic level on the corresponding input.

Features

• High Speed Operation: tpd (Clock to Q) = 17 ns typ (CL = 50 pF)

• High Output Current: Fanout of 10 LSTTL Loads

• Wide Operating Voltage: VCC = 2 to 6 V

• Low Input Current: 1 µA max

• Low Quiescent Supply Current: ICC (static) = 2 µA max (Ta = 25°C)

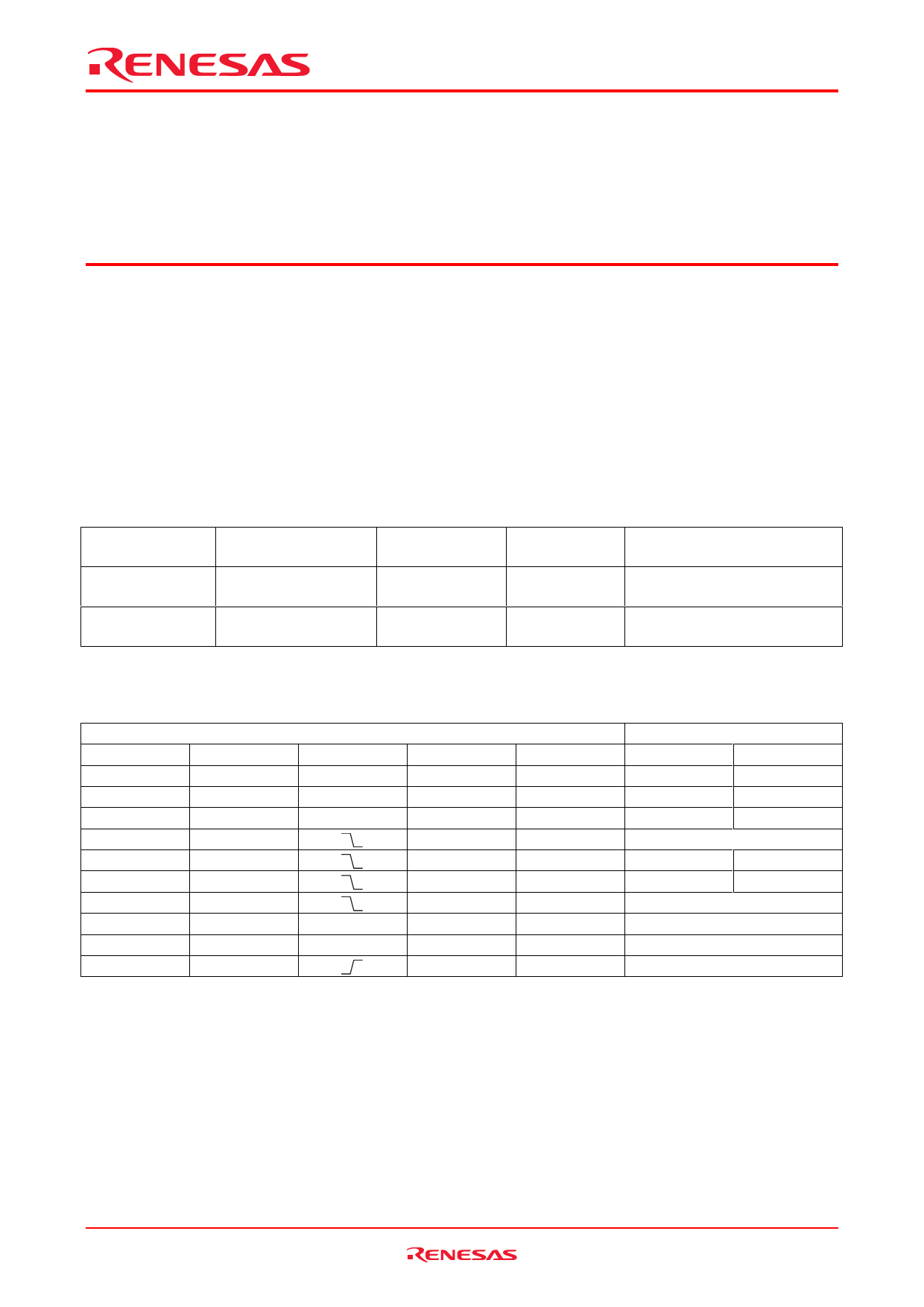

• Ordering Information

Part Name

Package Type

Package Code

(Previous Code)

Package

Abbreviation

HD74HC112P

DILP-16 pin

PRDP0016AE-B

(DP-16FV)

P

HD74HC112FPEL SOP-16 pin (JEITA)

PRSP0016DH-B

(FP-16DAV)

FP

Note: Please consult the sales office for the above package availability.

Taping Abbreviation

(Quantity)

—

EL (2,000 pcs/reel)

Function Table

Inputs

Outputs

Preset

Clear

Clock

J

K

Q

Q

L

H

X

X

X

H

L

H

L

X

X

X

L

H

L

L

X

X

X

H*1

H*1

H

H

L

L

No change

H

H

L

H

L

H

H

H

H

L

H

L

H

H

H

H

Toggle

H

H

L

X

X

No change

H

H

H

X

X

No change

H

H

X

X

No change

H : High level

L : Low level

X : Irrelevant

Note: 1. Q and Q will remain High as long as Preset and Clear are Low, but Q and Q are unpredictable, if Preset and

Clear go High simultaneously.

Rev.2.00, Oct 11, 2005 page 1 of 6