ADSP-2186NKCA-320 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

一致するリスト

ADSP-2186NKCA-320 Datasheet PDF : 45 Pages

| |||

ADSP-218xN Series

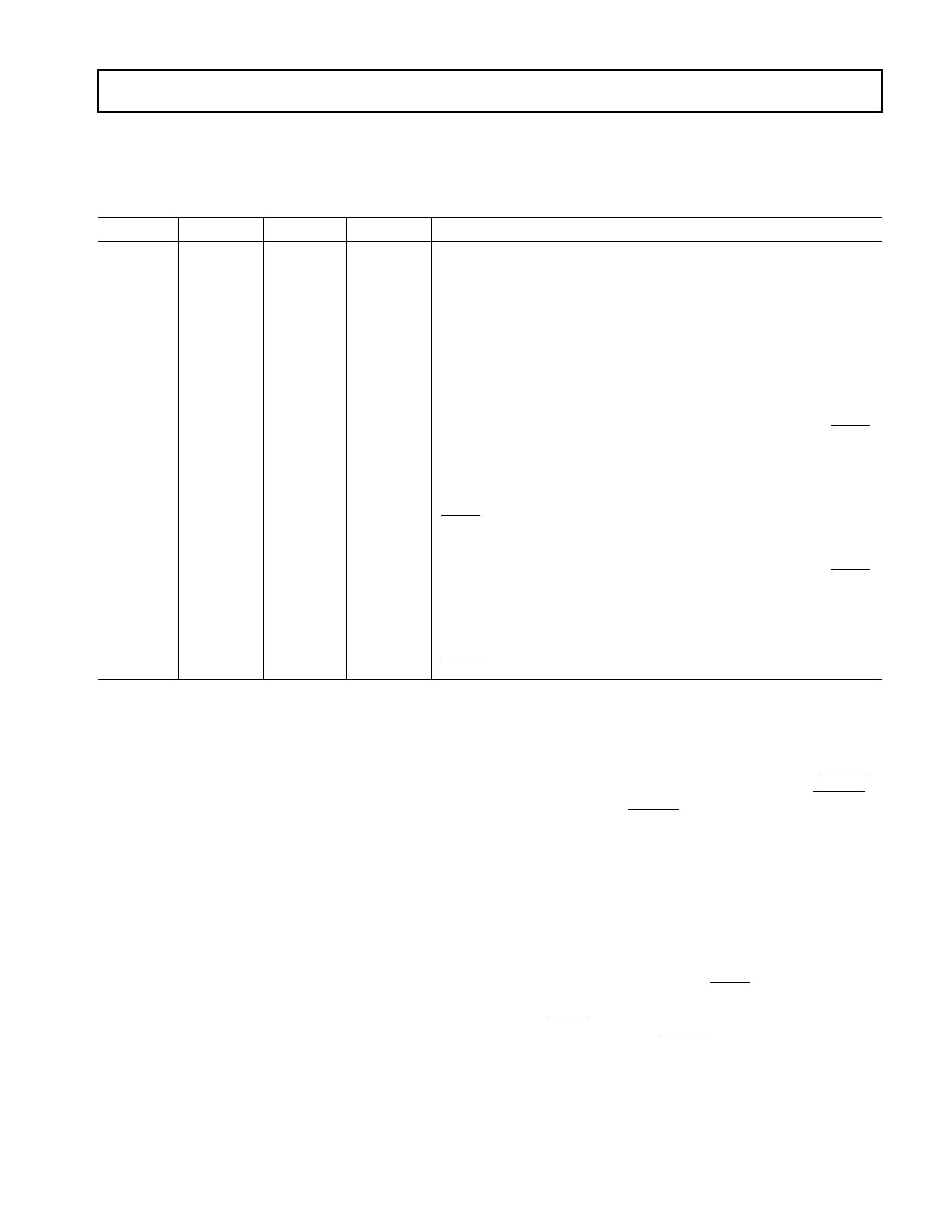

MODES OF OPERATION

The ADSP-218xN series modes of operation appear in

Table 7.

Table 7. Modes of Operation

Mode D Mode C Mode B Mode A Booting Method

X

0

0

0

BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Full Memory

Mode.1

X

0

1

0

No automatic boot operations occur. Program execution starts at

external memory location 0. Chip is configured in Full Memory

Mode. BDMA can still be used, but the processor does not automat-

ically use or wait for these operations.

0

1

0

0

BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Host Mode. IACK

has active pull-down. (Requires additonal hardware.)

0

1

0

1

IDMA feature is used to load any internal memory as desired.

Program execution is held off until the host writes to internal

program memory location 0. Chip is configured in Host Mode.

IACK has active pull-down.1

1

1

0

0

BDMA feature is used to load the first 32 program memory words

from the byte memory space. Program execution is held off until all

32 words have been loaded. Chip is configured in Host Mode; IACK

requires external pull-down. (Requires additonal hardware.)

1

1

0

1

IDMA feature is used to load any internal memory as desired.

Program execution is held off until the host writes to internal

program memory location 0. Chip is configured in Host Mode.

IACK requires external pull-down.1

1Considered as standard operating settings. Using these configurations allows for easier design and better memory management.

Setting Memory Mode

Memory Mode selection for the ADSP-218xN series is

made during chip reset through the use of the Mode C pin.

This pin is multiplexed with the DSP’s PF2 pin, so care must

be taken in how the mode selection is made. The two meth-

ods for selecting the value of Mode C are active and passive.

Passive Configuration

Passive Configuration involves the use of a pull-up or pull-

down resistor connected to the Mode C pin. To minimize

power consumption, or if the PF2 pin is to be used as

an output in the DSP application, a weak pull-up or pull-

down resistance, on the order of 10 k⍀, can be used. This

value should be sufficient to pull the pin to the desired level

and still allow the pin to operate as a programmable flag

output without undue strain on the processor’s output

driver. For minimum power consumption during power-

down, reconfigure PF2 to be an input, as the pull-up or pull-

down resistance will hold the pin in a known state, and will

not switch.

Active Configuration

Active Configuration involves the use of a three-statable

external driver connected to the Mode C pin. A driver’s

output enable should be connected to the DSP’s RESET

signal such that it only drives the PF2 pin when RESET is

active (low). When RESET is deasserted, the driver should

be three-state, thus allowing full use of the PF2 pin as either

an input or output. To minimize power consumption during

power-down, configure the programmable flag as an output

when connected to a three-stated buffer. This ensures that

the pin will be held at a constant level, and will not oscillate

should the three-state driver’s level hover around the logic

switching point.

IDMA ACK Configuration

Mode D = 0 and in host mode: IACK is an active, driven

signal and cannot be “wire ORed.” Mode D = 1 and in host

mode: IACK is an open drain and requires an external

pull-down, but multiple IACK pins can be “wire ORed”

together.

REV. 0

–11–