ADSP-21161NKCA-100 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

一致するリスト

ADSP-21161NKCA-100 Datasheet PDF : 60 Pages

| |||

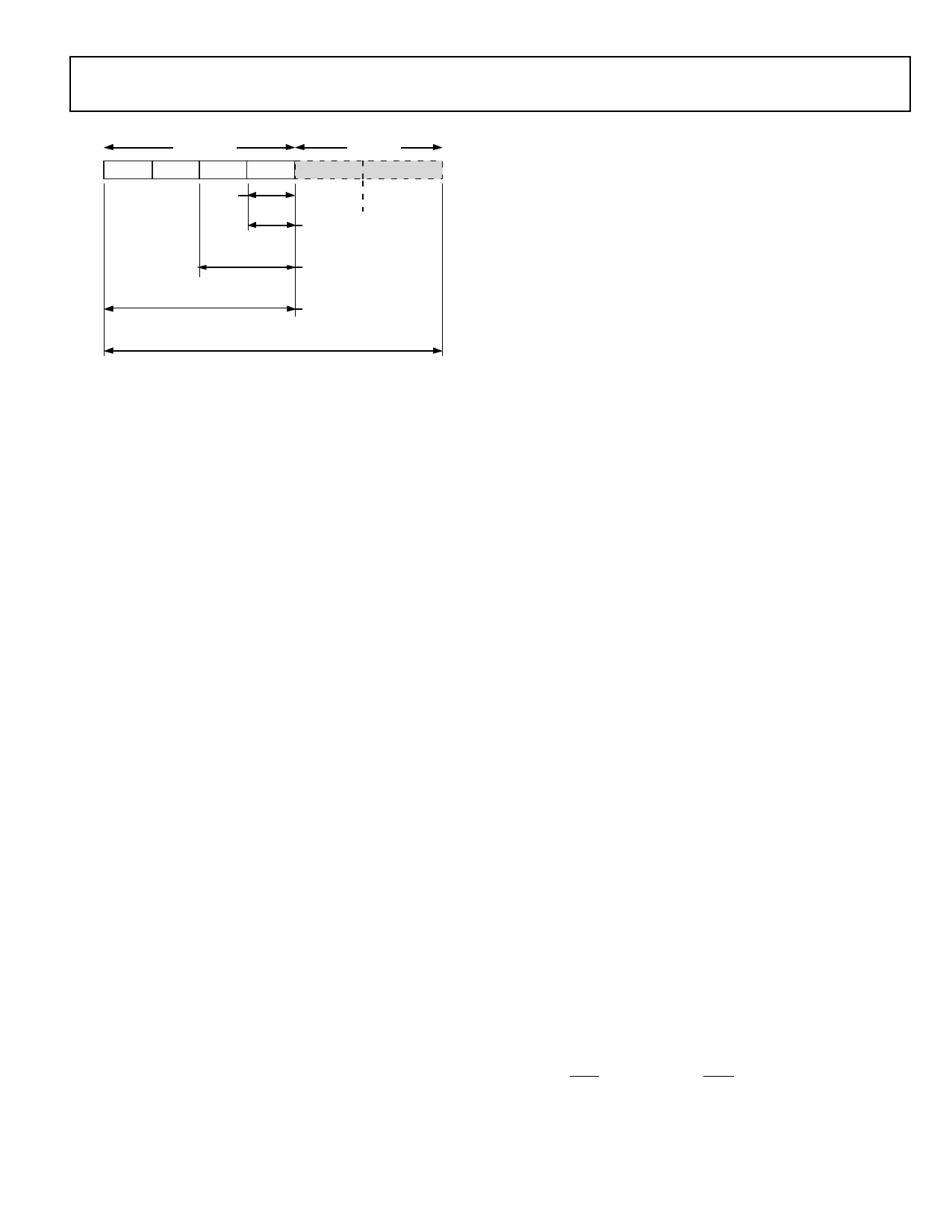

DATA47–16

DATA15–0

47 40 39 32 31 24 23 16 15

87

0

PROM

BO O T

L1DATA7–0 L0DATA7–0

DAT A15-8

DA TA7–0

8-BIT PACKED DMA D ATA

8-BIT PACKED INST RUCT ION

EX ECUTI ON

16-BIT PACKED DMA DATA

16-BIT PACKED INSTRUC-

TION EXECUTION

F LOAT OR FIXED, D31–D0,

32-BIT PA CKED

32-BIT PA CKED INSTRUC-

T ION

48-BIT INSTRUCT ION FETCH

NOTE:

(NO PACKING)

EXTRA DA TA LINES DATA15–0 AR E ONLY ACCESSIBLE IF LINK PORT S

ARE DISABLED. ENAB LE THESE ADDITIONAL DATA L INKS BY SELECT-

ING IPACK1–0 = 01 IN SYSCON.

Figure 4. External Data Alignment Options

Multiprocessing

The ADSP-21161N offers powerful features tailored to

multiprocessing DSP systems. The external port and link ports

provide integrated glueless multiprocessing support.

The external port supports a unified address space (see Figure 3)

that enables direct interprocessor accesses of each ADSP-

21161N’s internal memory-mapped (I/O processor) registers.

All other internal memory can be indirectly accessed via DMA

transfers initiated via the programming of the IOP DMA

parameter and control registers. Distributed bus arbitration

logic is included on-chip for simple, glueless connection of sys-

tems containing up to six ADSP-21161Ns and a host processor

(Figure 5). Master processor change over incurs only one cycle

of overhead. Bus arbitration is selectable as either fixed or rotat-

ing priority. Bus lock enables indivisible read-modify-write

sequences for semaphores. A vector interrupt is provided for

interprocessor commands. Using an instruction rate of

110 MHz, maximum throughput for interprocessor data trans-

fer is 440M bytes/s over the external port.

Two link ports provide a second method of multiprocessing

communications. Each link port can support communications

to another ADSP-21161N. The ADSP-21161N, running at

110 MHz, has a maximum throughput for interprocessor com-

munications over the links of 220M bytes/s. The link ports and

cluster multiprocessing can be used concurrently or

independently.

Link Ports

The ADSP-21161N features two 8-bit link ports that provide

additional I/O capabilities. With the capability of running at

110 MHz, each link port can support 110M bytes/s. Link port

I/O is especially useful for point-to-point interprocessor com-

munication in multiprocessing systems. The link ports can

operate independently and simultaneously, with a maximum

data throughput of 220M bytes/s. Link port data is packed into

48- or 32-bit words and can be directly read by the core proces-

sor or DMA-transferred to on-chip memory. Each link port has

ADSP-21161N

its own double-buffered input and output registers.

Clock/acknowledge handshaking controls link port transfers.

Transfers are programmable as either transmit or receive.

Serial Ports

The ADSP-21161N features four synchronous serial ports that

provide an inexpensive interface to a wide variety of digital and

mixed-signal peripheral devices. Each serial port is made up of

two data lines, a clock and frame sync. The data lines can be

programmed to either transmit or receive.

The serial ports operate at up to half the clock rate of the core,

providing each with a maximum data rate of 55M bit/s. The

serial data pins are programmable as either a transmitter or

receiver, providing greater flexibility for serial communications.

Serial port data can be automatically transferred to and from

on-chip memory via a dedicated DMA. Each of the serial ports

features a Time Division Multiplex (TDM) multichannel mode,

where two serial ports are TDM transmitters and two serial

ports are TDM receivers (SPORT0 Rx paired with SPORT2 Tx,

SPORT1 Rx paired with SPORT3 Tx). Each of the serial ports

also support the I2S protocol (an industry standard interface

commonly used by audio codecs, ADCs and DACs), with two

data pins, allowing four I2S channels (using two I2S stereo

devices) per serial port, with a maximum of up to 16 I2S chan-

nels. The serial ports permit little-endian or big-endian

transmission formats and word lengths selectable from 3 bits to

32 bits. For I2S mode, data-word lengths are selectable between

8 bits and 32 bits. Serial ports offer selectable synchronization

and transmit modes as well as optional μ-law or A-law com-

panding. Serial port clocks and frame syncs can be internally or

externally generated.

Serial Peripheral (Compatible) Interface

Serial Peripheral Interface (SPI) is an industry standard syn-

chronous serial link, enabling the ADSP-21161N SPI-

compatible port to communicate with other SPI-compatible

devices. SPI is a 4-wire interface consisting of two data pins, one

device select pin, and one clock pin. It is a full-duplex synchro-

nous serial interface, supporting both master and slave modes.

The SPI port can operate in a multimaster environment by

interfacing with up to four other SPI-compatible devices, either

acting as a master or slave device. The ADSP-21161N SPI-com-

patible peripheral implementation also features programmable

baud rate and clock phase/polarities. The ADSP-21161N SPI-

compatible port uses open drain drivers to support a multimas-

ter configuration and to avoid data contention.

Host Processor Interface

The ADSP-21161N host interface enables easy connection to

standard 8-bit, 16-bit, or 32-bit microprocessor buses with little

additional hardware required. The host interface is accessed

through the ADSP-21161N’s external port. Four channels of

DMA are available for the host interface; code and data transfers

are accomplished with low software overhead. The host proces-

sor requests the ADSP-21161N’s external bus with the host bus

request (HBR), host bus grant (HBG), and chip select (CS) sig-

nals. The host can directly read and write the internal IOP

registers of the ADSP-21161N, and can access the DMA channel

Rev. C | Page 7 of 60 | January 2013