AD73360AR データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

一致するリスト

AD73360AR Datasheet PDF : 35 Pages

| |||

AD73360

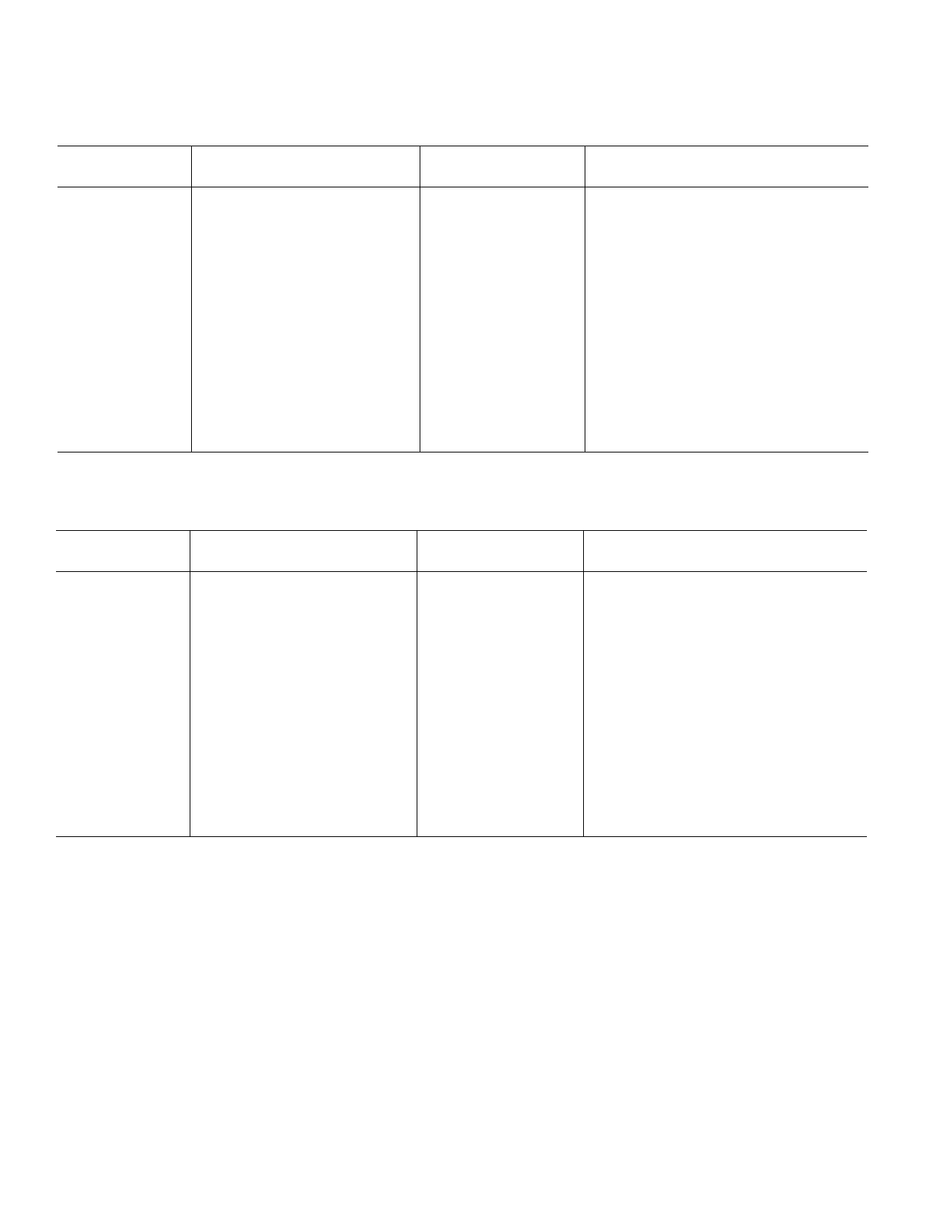

TIMING CHARACTERISTICS (AVDD = 3 V ؎ 10%; DVDD = 3 V ؎ 10%; AGND = DGND = 0 V; TA = TMlN to TMAX, unless otherwise

noted)

Parameter

Clock Signals

t1

t2

t3

Serial Port

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

Limit at

TA = –40؇C to +85؇C

61

24.4

24.4

t1

0.4 × t1

0.4 × t1

20

0

10

10

10

10

30

Unit

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns max

ns min

ns min

ns max

ns max

Description

See Figure 1

MCLK Period

MCLK Width High

MCLK Width Low

See Figures 3 and 4

SCLK Period

SCLK Width High

SCLK Width Low

SDI/SDIFS Setup Before SCLK Low

SDI/SDIFS Hold After SCLK Low

SDOFS Delay from SCLK High

SDOFS Hold After SCLK High

SDO Hold After SCLK High

SDO Delay from SCLK High

SCLK Delay from MCLK

TIMING CHARACTERISTICS (AVDD = 5 V ؎ 10%; DVDD = 5 V ؎ 10%; AGND = DGND = 0 V; TA = TMlN to TMAX, unless otherwise

noted)

Parameter

Clock Signals

t1

t2

t3

Serial Port

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

Limit at

TA = –40؇C to +85؇C

61

24.4

24.4

t1

0.4 × t1

0.4 × t1

20

0

10

10

10

10

30

Unit

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns max

ns min

ns min

ns max

ns max

Description

See Figure 1

MCLK Period

MCLK Width High

MCLK Width Low

See Figures 3 and 4

SCLK Period

SCLK Width High

SCLK Width Low

SDI/SDIFS Setup Before SCLK Low

SDI/SDIFS Hold After SCLK Low

SDOFS Delay from SCLK High

SDOFS Hold After SCLK High

SDO Hold After SCLK High

SDO Delay from SCLK High

SCLK Delay from MCLK

–6–

REV. A