W83194BR-138 データシートの表示(PDF) - Winbond

部品番号

コンポーネント説明

一致するリスト

W83194BR-138 Datasheet PDF : 14 Pages

| |||

W83194BR-138

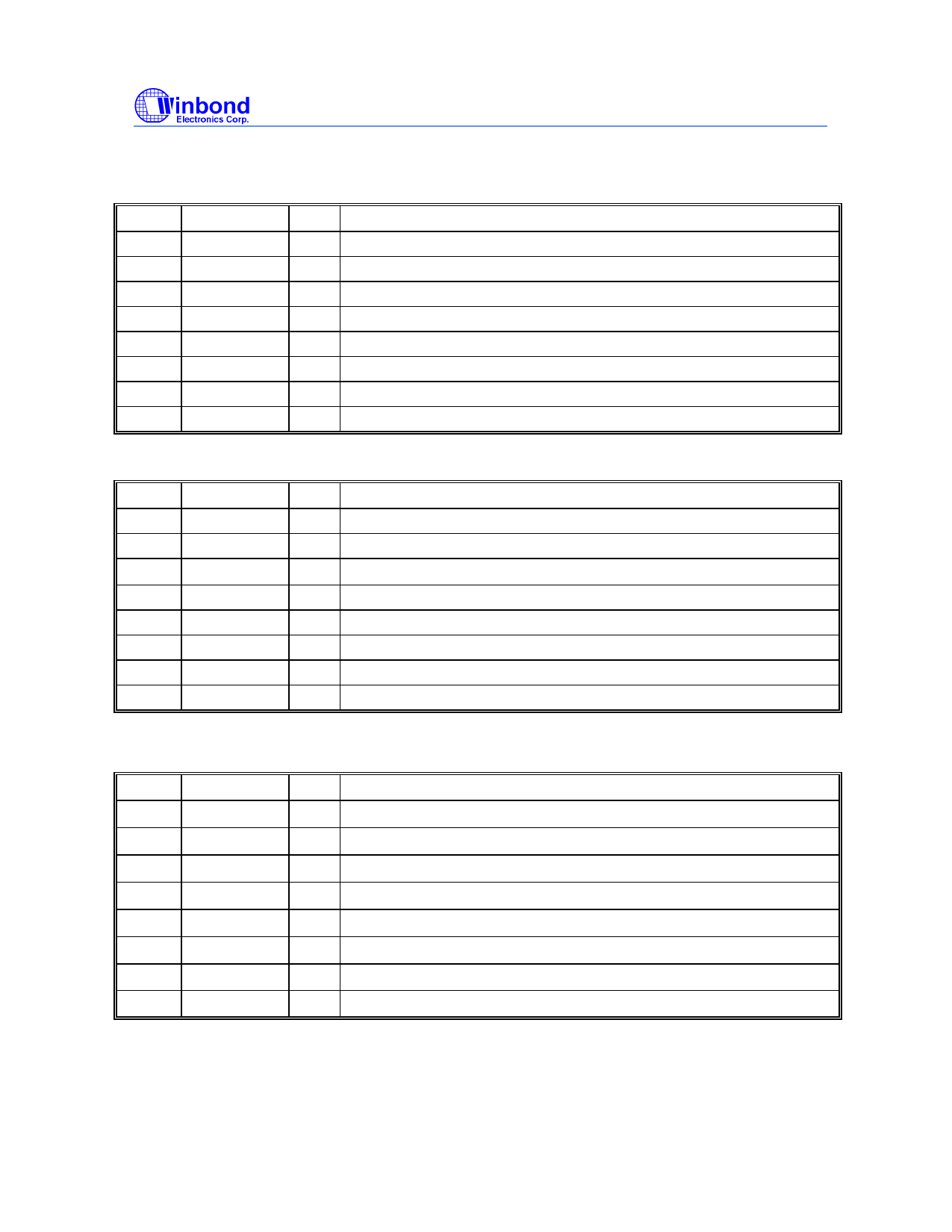

5.4 Register 3: PCI Clock Register (1 = Active, 0 = Inactive)

Bit @PowerUp Pin

Description

7

1

31 SDRAM_F (Active / Inactive)

6

1

20 PCICLK6 (Active / Inactive)

5

1

19 PCICLK5 (Active / Inactive)

4

1

17 PCICLK4 (Active / Inactive)

3

1

16 PCICLK3 (Active / Inactive)

2

1

15 PCICLK2 (Active / Inactive)

1

1

13 PCICLK1 (Active / Inactive)

0

1

12 PCICLK0 (Active / Inactive)

5.5 Register 4: Additional Register (1 = Active, 0 = Inactive)

Bit @PowerUp Pin

Description

7

1

9 3V66_2(Active / Inactive)

6

1

8 3V66_1(Active / Inactive)

5

1

7 3V66_0(Active / Inactive)

4

1

28 24_48MHz(Active / Inactive)

3

1

47 IOAPIC(Active / Inactive)

2

1

27 48MHz_0(Active / Inactive)

1

1

26 48MHz_1(Active / Inactive)

0

1

1 REF0 (Active / Inactive)

PRELIMINARY

5.6 Register 5: SDRAM Clock Register (1 = Active, 0 = Inactive)

Bit @PowerUp Pin

Description

7

1

- CSkew2 (CPU to SDRAM skew program bit)

6

0

- CSkew1 (CPU to SDRAM skew program bit)

5

0

- CSkew0 (CPU to SDRAM skew program bit)

4

1

- CASkew2 (CPU to 3V66 skew program bit)

3

0

- CASkew1 (CPU to 3V66 skew program bit)

2

0

- CASkew0 (CPU to 3V66 skew program bit)

1

1

44 CPUCLK1(Active / Inactive)

0

1

45 CPUCLK0(Active / Inactive)

Publication Release Date: May 2000

-9-

Revision 0.37