MC74HC354 データシートの表示(PDF) - Motorola => Freescale

部品番号

コンポーネント説明

一致するリスト

MC74HC354

MC74HC354 Datasheet PDF : 9 Pages

| |||

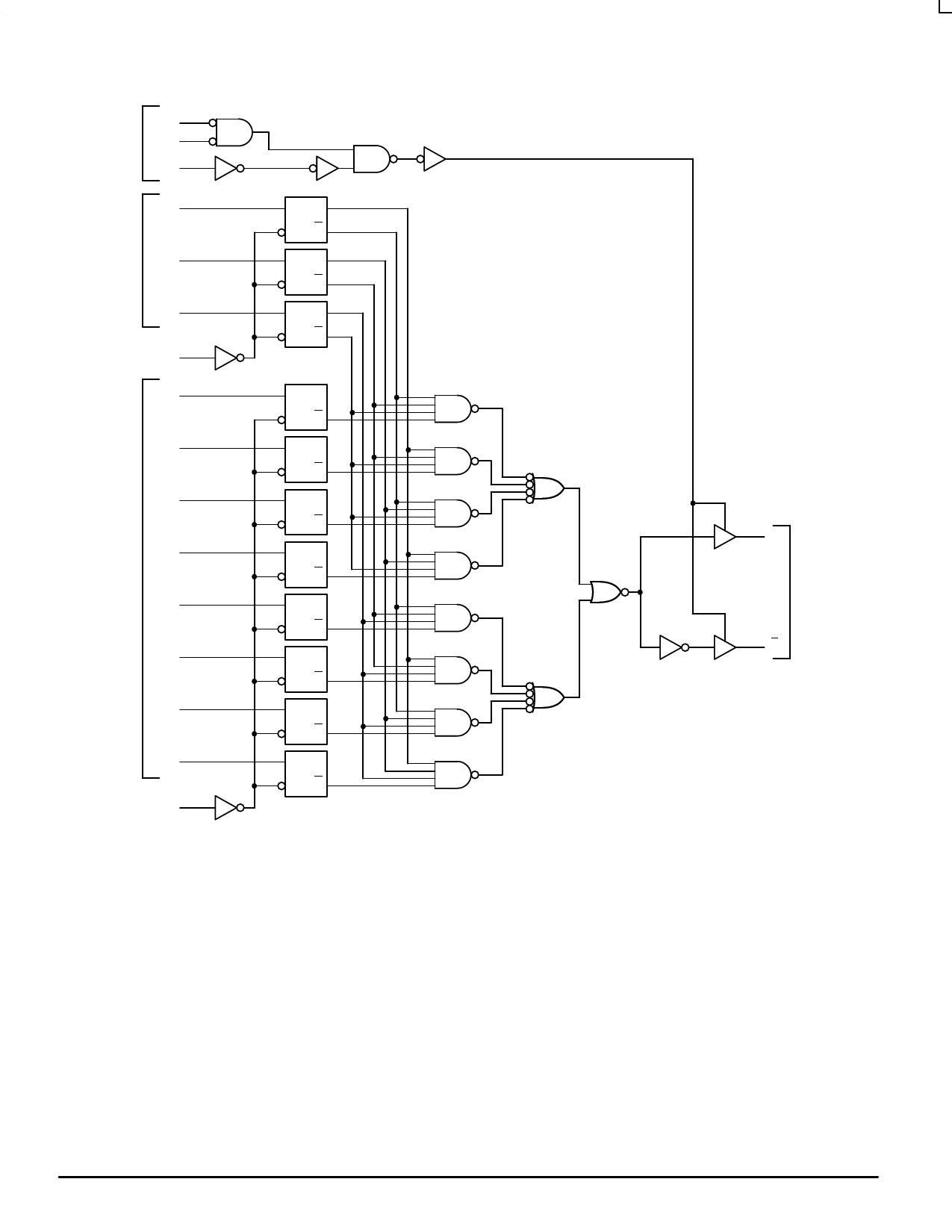

Output

Enables

OE1 15

OE2 16

OE3 17

A0 14

Address

Inputs

A1 13

A2 12

Address– 11

Latch Enable

D0 8

D1 7

D2 6

Data

Inputs

D3 5

D4 4

D5 3

D6 2

D7 1

Data–Latch 9

Enable

DQ

LE Q

DQ

LE Q

DQ

LE Q

D

LE Q

D

LE Q

D

LE Q

D

LE Q

D

LE Q

D

LE Q

D

LE Q

D

LE Q

Figure 8. Expanded Logic Diagram

MC54/74HC354

19 Y

3–State

Data

Outputs

18 Y

High–Speed CMOS Logic Data

7

DL129 — Rev 6

MOTOROLA