CS5451A-IS データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

CS5451A-IS Datasheet PDF : 14 Pages

| |||

CS5451A

CS5451A typical inputs and power supply connec-

tions.

3.2 Performing Measurements

The converter outputs are transferred in 16-bit

signed (two’s complement) data formats as a per-

centage of full scale. Table 1 below illustrates the

ideal relationship between the differential voltage

presented to any one of the input channels and the

corresponding output code. Note that for the cur-

rent channels, the state of the GAIN input pin is as-

sumed to driven low such that the PGA gain on the

current channels is 1x. If the PGA gain of the cur-

rent channels is set to 20x, a +40 mV differential

voltage is presented across any pair of “IINk+” and

“IINk-” pins (k = 1, 2, 3) would cause a (nominal)

output code of 32767.

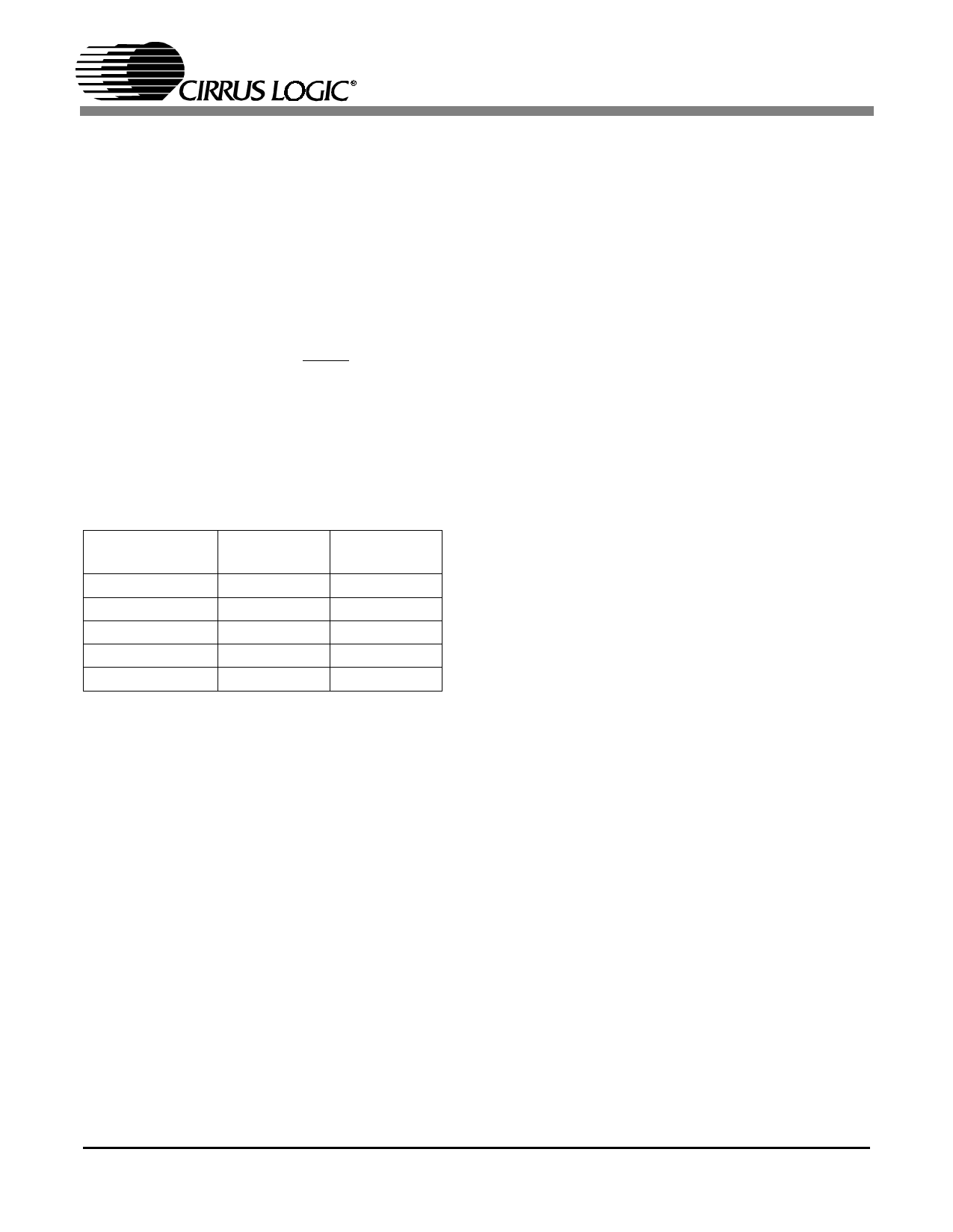

Differential Input Output Code Output Code

Voltage (mV) (hexadecimal) (decimal)

+800

7FFF

32767

0.0122 to 0.0366

0001

1

-0.0122 to 0.0122

0000

0

-0.0122 to -0.0366

FFFF

-1

-800

8000

-32768

Table 1. Nominal Relationship for Differential Input

Voltage vs. Output Code, for all channels. (Assume PGA

gain is set to 1x.)

3.3 High Rate Digital Filters

If the OWRS pin is set to logic low, the high-rate

filters are implemented as fixed sinc3 filters with

the following transfer function:

H(z)

=

-1----–-----z--–---2---5--6-

3

1 – z–1

This filter samples the modulator bit stream at

XIN/8 Hz and decimates to XIN/2048 Hz.

If the OWRS pin is set to logic high, then the trans-

fer function is

H(z)

=

1-----–----z---–---1---2--8-

3

1 – z–1

The above filter samples the modulator bit stream

at XIN/8 Hz and decimates to XIN/1024 Hz.

3.4 Serial Interface

The CS5451A communicates with a target device

via a master serial data output port. Output data is

provided on the SDO output synchronous with the

SCLK output. A third output, FSO, is a framing

signal used to signal the start of output data. These

three outputs will be driven as long as the SE (serial

enable) input is held high. Otherwise, these outputs

will be high impedance.

Data out (SDO) changes as a result of SCLK fall-

ing, and always outputs valid data with SCLK ris-

ing. When data is being transferred, the SCLK

frequency is either 1/8 of the XIN input frequency

(when OWRS is held low) or 1/4 of the XIN input

frequency (when OWRS is held high). Any other

time, SCLK is held low. (See Figures 3 and 4.)

The framing signal (FSO) output is normally low,

but produces a high level pulse lasting one SCLK

period when the instantaneous voltage/current data

samples are about to be transmitted out of the serial

10

DS635PP1