CS4610C-CQ データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

CS4610C-CQ Datasheet PDF : 29 Pages

| |||

CS4610/11

CrystalClear™ SoundFusion™ PCI Audio Accelerator

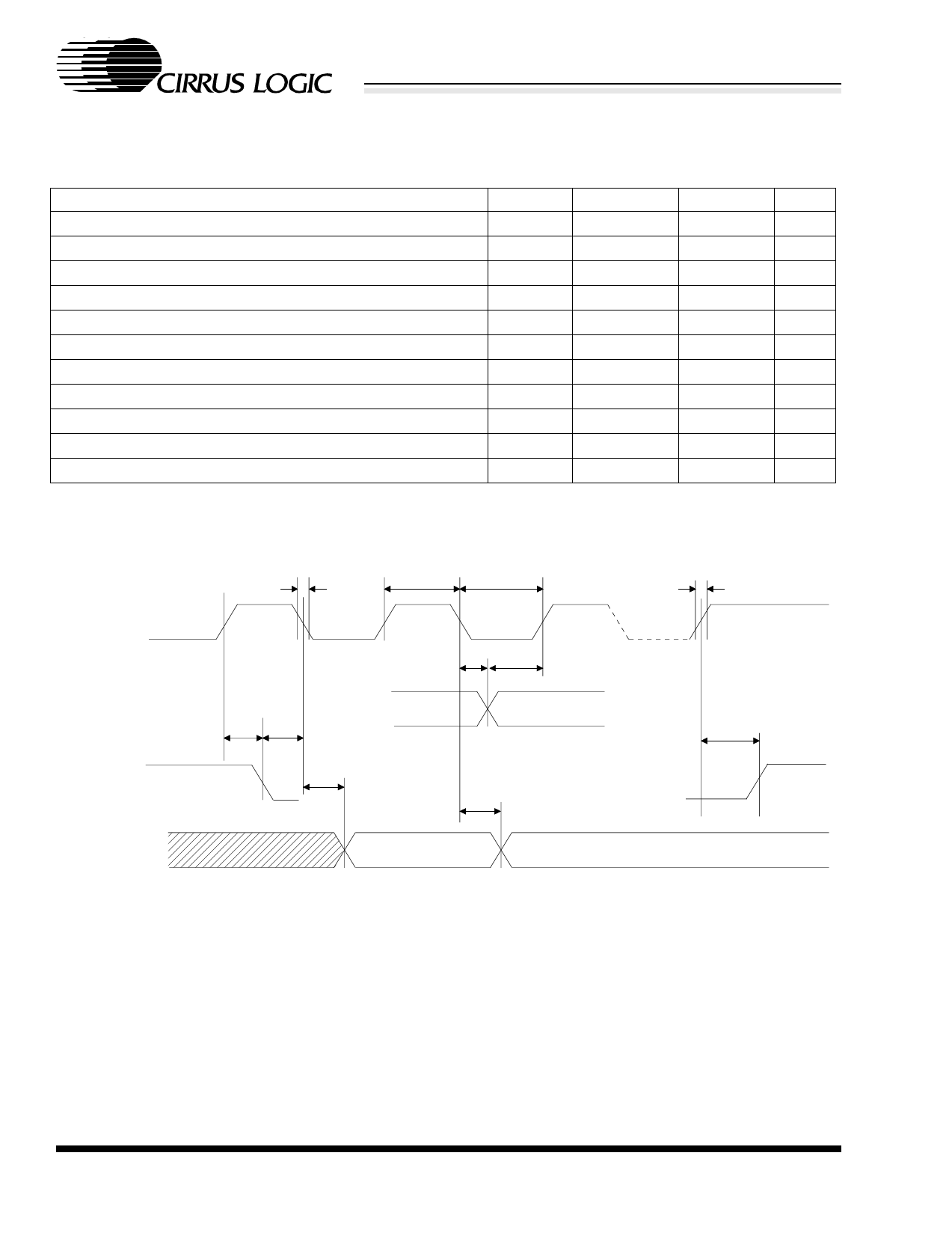

EEPROM TIMING CHARACTERISTICS Note 4. (TA = 0 to 70 °C, PCIVDD = CVDD = CRYVDD =

3.3 V; VDD5REF = 5 V; VDD5REF = 5 V; PCIGND = CGND = CRYGND = 0 V; Logic 0 = 0 V, Logic 1 = 3.3 V;

Timing reference levels = 1.4 V; PCI clock frequency = 33 MHz; unless otherwise noted)

Parameter

Symbol

Min

EECLK Low to EEDAT Data Out Valid

tAA

0

Start Condition Hold Time

tHD:STA

5.0

EECLK Low

tLEECLK

10

EECLK High

tHEECLK

10

Start Condition Setup Time (for a Repeated Start Condition)

tSU:STA

5.0

EEDAT In Hold Time

tHD:DAT

0

EEDAT In Setup Time

tSU:DAT

250

EEDAT/EECLK Rise Time

(Note 16)

tR

-

EEDAT/EECLK Fall Time

tF

-

Stop Condition Setup Time

tSU:STO

5.0

EEDAT Out Hold Time

tDH

0

Max

Units

7.0

µs

-

µs

-

µs

-

µs

-

µs

-

µs

-

ns

1

µs

300

ns

-

µs

-

µs

Notes: 16. Rise time on EEDAT is determined by the capacitance on the EEDAT line with all connected gates and

the required external pull-up resistor.

EECLK

EEDAT (IN)

t SU:STA

EEDAT (OUT)

EEDAT (OUT)

tF

t HEECLK

t LEECLK

t HD:STA

t AA

t

HD:DAT

t DH

t SU:DAT

tR

t SU:STO

Figure 5. EEPROM Timing

8

DS241PP5