CS44L10 データシートの表示(PDF) - Cirrus Logic

部品番号

コンポーネント説明

一致するリスト

CS44L10 Datasheet PDF : 34 Pages

| |||

CS44L10

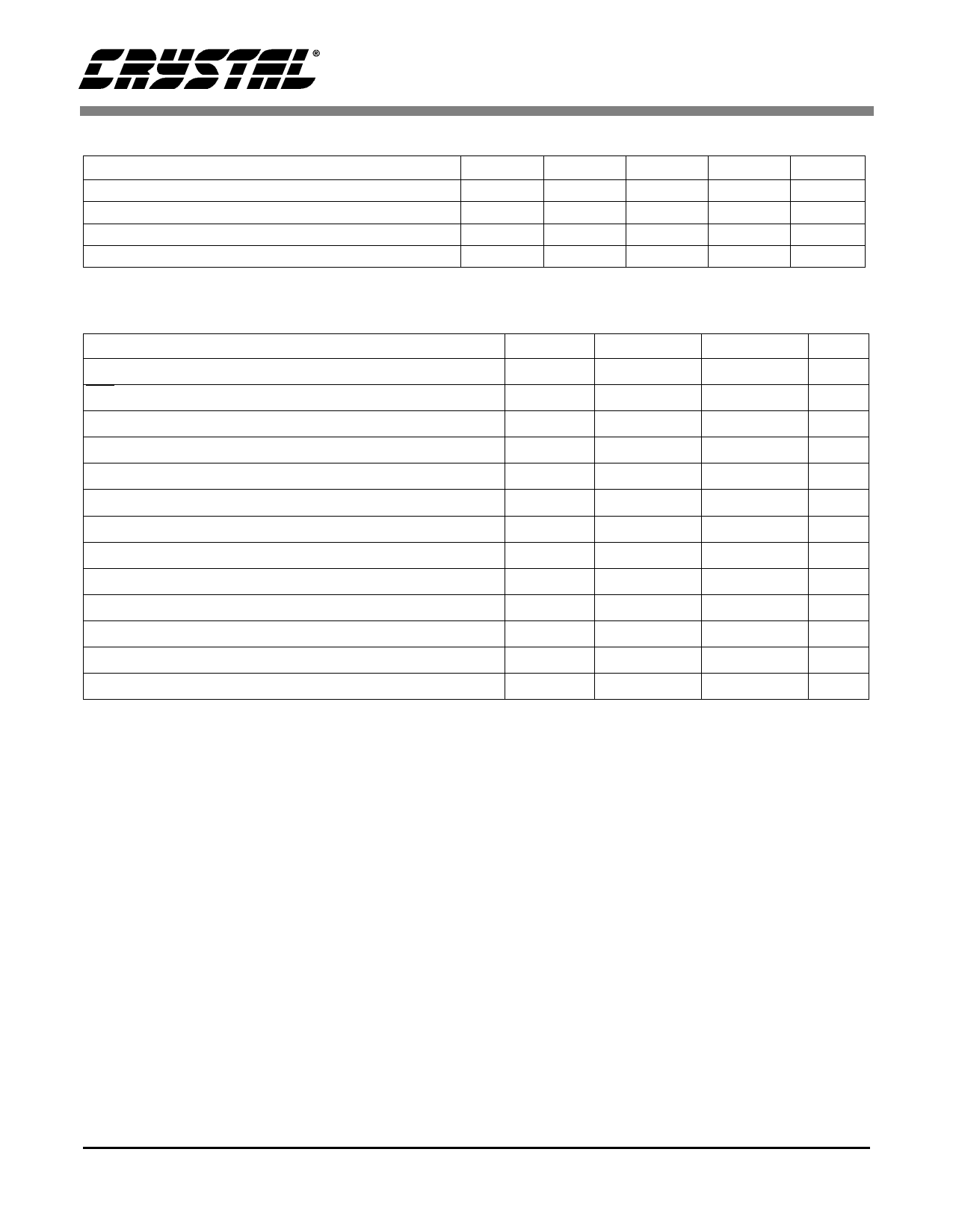

DIGITAL CHARACTERISTICS (TA = 25° C; VL = 2.4 V - 3.6 V; GND = 0 V)

Parameters

Symbol

Min

Typ

High-Level Input Voltage

Low-Level Input Voltage

Input Leakage Current

Input Capacitance

VIH

0.7 x VL

-

VIL

-

-

Iin

-

-

-

8

Max

-

0.3 x VL

±10

-

Units

V

V

µA

pF

SWITCHING CHARACTERISTICS- CONTROL PORT- TWO-WIRE FORMAT

(Note 7) (TA = 25° C; VL = 2.4 V - 5.0 V; Inputs: Logic 0 = GND, Logic 1 = VL, CL = 30 pF)

Parameter

Symbol

Min

Max

Unit

SCL Clock Frequency

fscl

-

100

kHz

RST Rising Edge to Start

tirs

500

-

ns

Bus Free Time Between Transmissions

tbuf

4.7

-

µs

Start Condition Hold Time (prior to first clock pulse)

thdst

4.0

-

µs

Clock Low time

tlow

4.7

-

µs

Clock High Time

thigh

4.0

-

µs

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling

tsust

4.7

(Note 8)

thdd

0

-

µs

-

µs

SDA Setup time to SCL Rising

tsud

250

-

ns

Rise Time of SCL and SDA

trc, trc

-

1

µs

Fall Time SCL and SDA

tfc, tfc

-

300

ns

Setup Time for Stop Condition

Acknowledge Delay from SCL Falling

(Note 9)

tsusp

tack

4.7

-

µs

-

(Note 10)

ns

Note:

7. The Two-Wire Format is compatible with the I2C protocol.

8. Data must be held for sufficient time to bridge the transition time, tfc, of SCL.

9. The acknowledge delay is based on MCLK and can limit the maximum transaction speed.

10. ----------5---------- for Single-Speed Mode and ----------5----------- for Double-Speed Mode.

256 × Fs

128 × Fs

8

DS541PP1