FM24C64VN データシートの表示(PDF) - Fairchild Semiconductor

部品番号

コンポーネント説明

一致するリスト

FM24C64VN Datasheet PDF : 13 Pages

| |||

Read Operations

Read operations are initiated in the same manner as write

operations, with the exception that the R/W bit of the slave

address is set to a one. There are three basic read operations:

current address read, random read, and sequential read.

Current Address Read

Internally the FM24C64 contains an address counter that main-

tains the address of the last byte accessed, incremented by one.

Therefore, if the last access (either a read or write) was to address

n, the next read operation would access data from address n + 1.

Upon receipt of the slave address with R/W set to "1," the

FM24C64 issues an acknowledge and transmits the eight bit

word. The master will not acknowledge the transfer but does

generate a stop condition, and therefore the FM24C64 discontin-

ues transmission. Refer Figure 6 for the sequence of address,

acknowledge and data transfer.

Random Read

Random read operations allow the master to access any memory

location in a random manner. Prior to issuing the slave address

with the R/W bit set to "1," the master must first perform a

“dummy” write operation. The master issues the start condition,

slave address with the R/W bit set to "0" and then the byte

address. After the byte address acknowledge, the master imme-

diately issues another start condition and the slave address with

the R/W bit set to one. This will be followed by an acknowledge

from the FM24C64 and then by the eight bit word. The master will

not acknowledge the transfer but does generate the stop condi-

tion, and therefore the FM24C64 discontinues transmission.

Refer Figure 7 for the address, acknowledge, and data transfer

sequence.

Sequential Read

Sequential reads can be initiated as either a current address read

or random access read. The first word is transmitted in the same

manner as the other read modes; however, the master now

responds with an acknowledge, indicating it requires additional

data. The FM24C64 continues to output data for each acknowl-

edge received. The read operation is terminated by the master not

responding with an acknowledge or by generating a stop condi-

tion.

The data output is sequential with the data from address n

followed by the data from n + 1. The address counter for read

operations increments all word address bits, allowing the entire

memory contents to be serially read during one operation. After

the entire memory has been read, the counter "rolls over" to the

beginning of the memory. FM24C64 continues to output data for

each acknowledge received. Refer Figure 8 for the address,

acknowledge, and data transfer sequence.

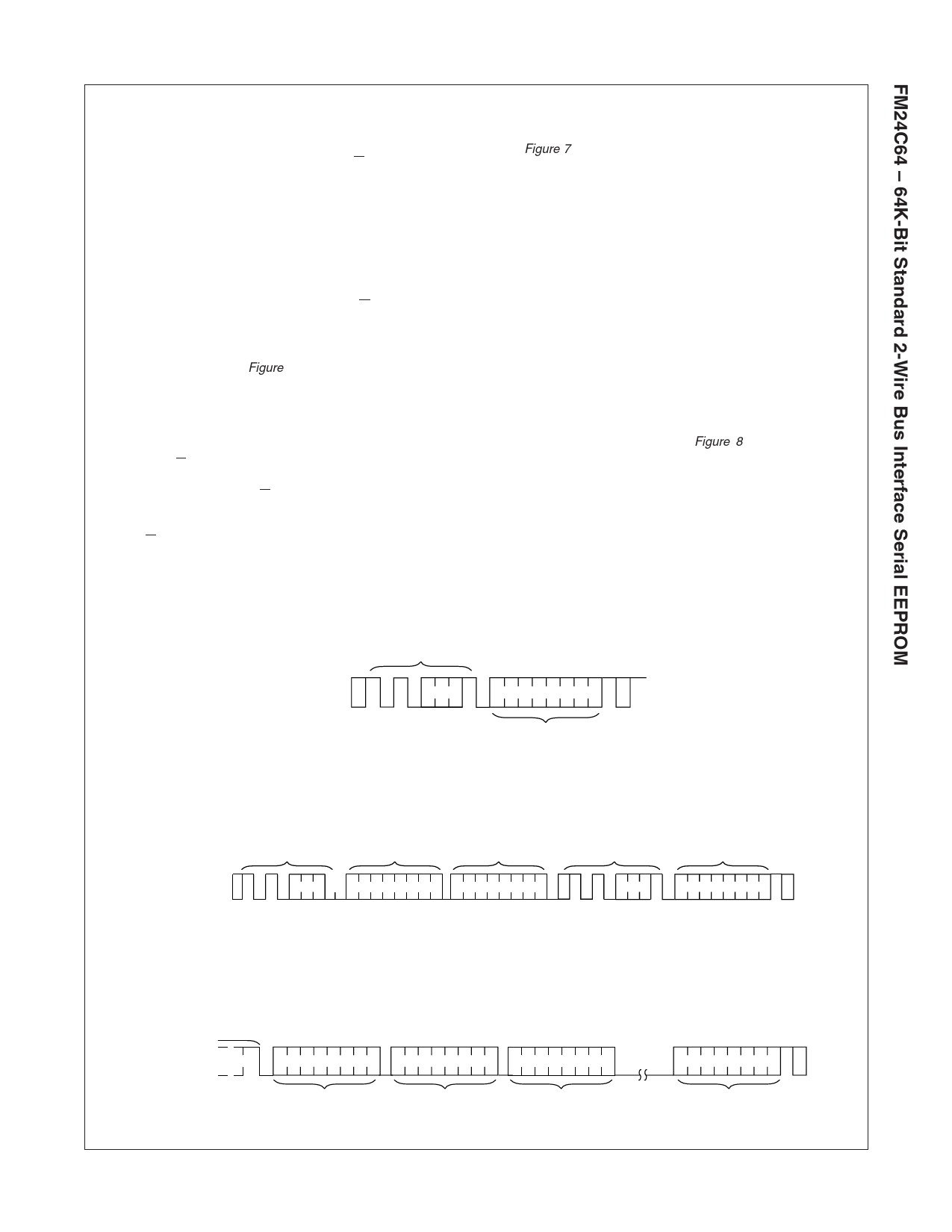

Current Address Read (Figure 6)

S

T

S

Bus Activity:

A

SLAVE

T

Master

R ADDRESS

O

T

P

SDA Line

101 0

1

Bus Activity:

EEPROM

A

NO

C

DATA

A

K

C

K

Random Read (Figure 7)

S

T

Bus Activity:

A

R

Master T

SLAVE

ADDRESS

WORD

ADDRESS (1)

WORD

ADDRESS (0)

S

T

A SLAVE

R ADDRESS

T

S

T

DATA

O

P

SDA Line

Bus Activity:

EEPROM

0

A

A

A

C

C

C

K

K

K

1

A

NO

C

A

K

C

K

Sequential Read (Figure 8)

Bus Activity:

Master

Slave

Address

SDA Line

Bus Activity:

EEPROM

A

C

DATA n +1

K

A

A

A

C

C

C

K

K

K

DATA n +1

DATA n + 2

S

T

O

P

NO

DATA n + x

A

C

K

FM24C64 Rev. C

11

www.fairchildsemi.com