DM9102 データシートの表示(PDF) - Davicom Semiconductor, Inc.

部品番号

コンポーネント説明

一致するリスト

DM9102 Datasheet PDF : 63 Pages

| |||

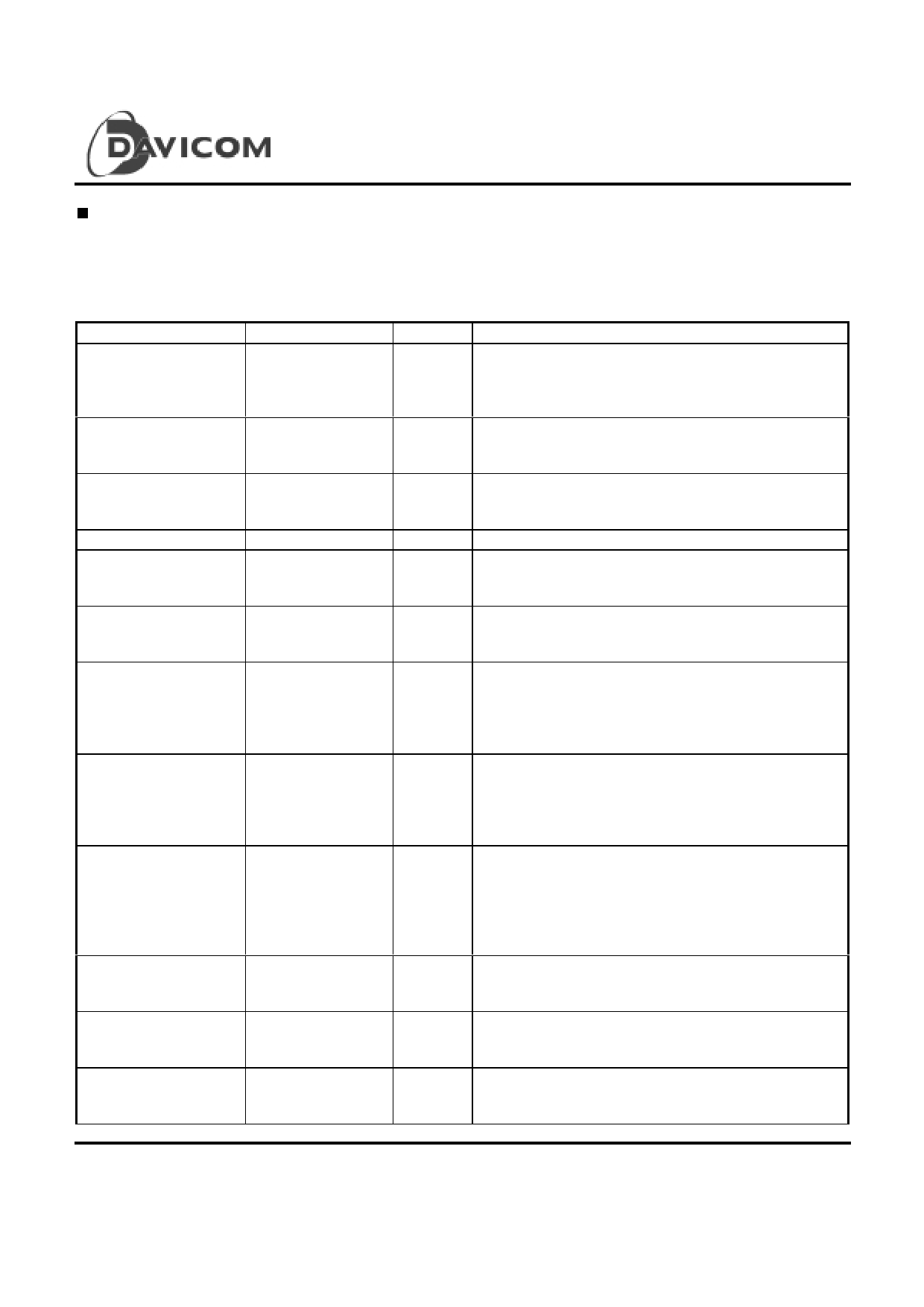

T Pin Description

DM9102

10/100Mbps Single Chip LAN Controller

I = Input, O = Output, I/O = Input/Output, O/D = Open Drain, P = Power

LI = reset Latch Input, # = all pin name with # are asserted Low

PCI Bus Interface

Pin No.

1

4

5

6

20

34

37

38

40

41

42

43

Pin Name

PCLK

GNT#

REQ#

NC

IDSEL

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

PERR#

SERR#

I/O

Description

I

PCI system clock

PCI bus clock that provides timing for DM9102 related to

PCI bus transactions. The clock frequency range is up to

33MHz.

I

Bus Grant

This signal is asserted low to indicate that DM9102 has

been granted ownership of the bus by the central arbiter.

O

Bus Request

The DM9102 will assert this signal low to request the

ownership of the bus.

No Connection

I

Initialization Device Select

This signal is asserted high during Configuration Space

read and write access.

I/O Cycle Frame

This signal is driven low by the DM9102 master mode to

indicate the beginning and duration of a bus transaction.

I/O Initiator Ready

This signal is driven low when the master is ready to

complete the current data phase of the transaction. A data

phase is completed on any clock both IRDY# and TRDY#

are sampled asserted.

I/O Target Ready

This signal is driven low when the target is ready to

complete the current data phase of the transaction. During

a read, it indicates that valid data is asserted. During a

write, it indicates the target is prepared to accept data.

I/O Device Select

The DM9102 asserts the signal low when it recognizes its

target address after FRAME# is asserted. As a bus

master, the DM9102 will sample this signal to insure that

the destination address for the data transfer is recognized

by a target.

I/O Stop

This signal is asserted low by the target device to request

the master device to stop the current transaction.

I/O Parity Error

The DM9102 as a master or slave will assert this signal

low to indicate a parity error on any incoming data.

I/O System Error

This signal is asserted low when an address parity is

detected with PCICS bit31 (detected parity error) Is

6

Final

Version: DM9102-DS-F03

August 30, 2000