M24C64R4BN5T データシートの表示(PDF) - STMicroelectronics

部品番号

コンポーネント説明

一致するリスト

M24C64R4BN5T Datasheet PDF : 26 Pages

| |||

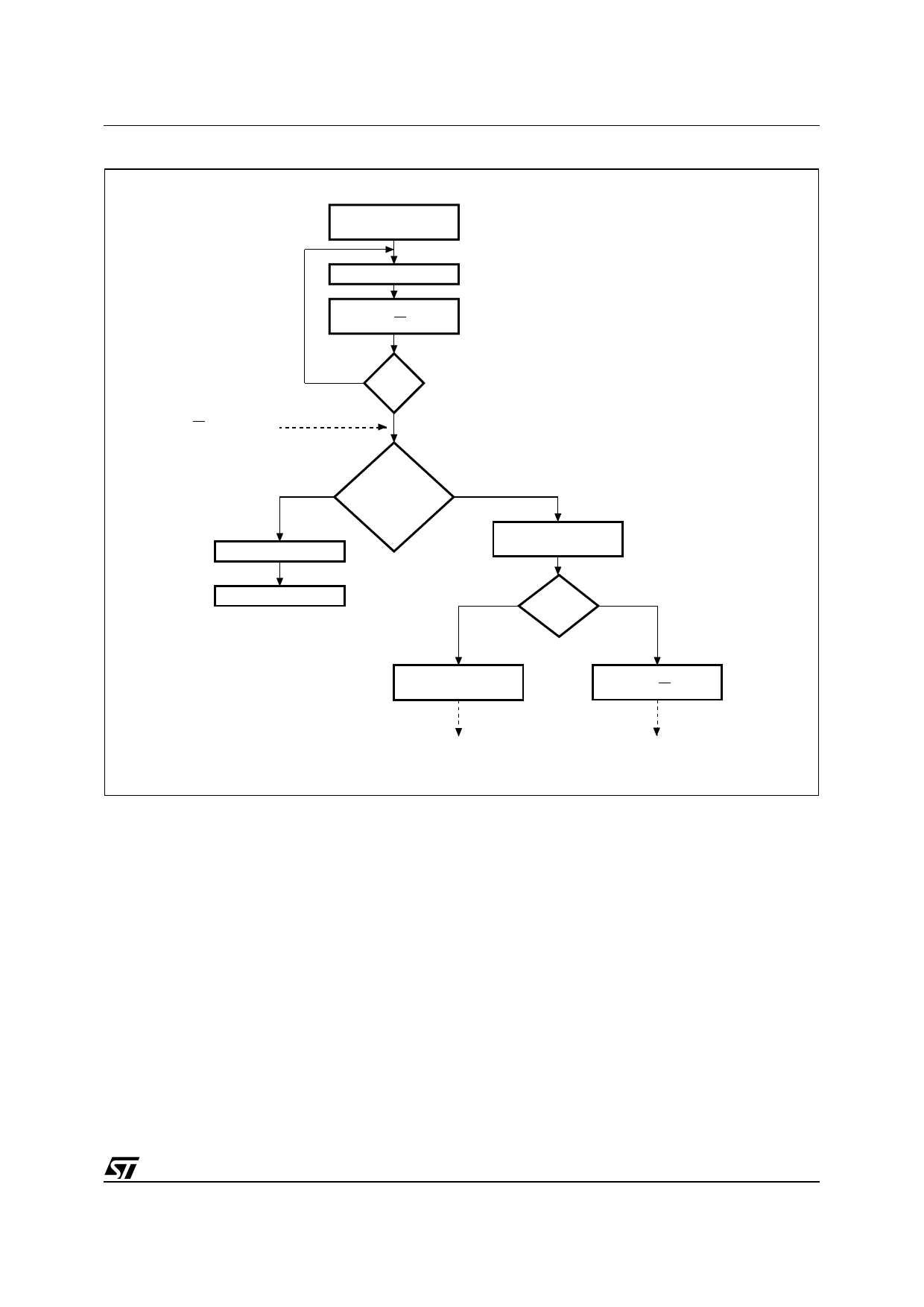

Figure 9. Write Cycle Polling Flowchart using ACK

M24C64, M24C32

WRITE Cycle

in Progress

START Condition

DEVICE SELECT

with RW = 0

First byte of instruction

with RW = 0 already

decoded by the device

NO ACK

Returned

YES

Next

NO

Operation is

Addressing the

Memory

ReSTART

YES

Send Address

and Receive ACK

STOP

NO

START

YES

Condition

DATA for the

WRITE Operation

DEVICE SELECT

with RW = 1

Continue the

WRITE Operation

Continue the

Random READ Operation

AI01847C

Minimizing System Delays by Polling On ACK

During the internal Write cycle, the device discon-

nects itself from the bus, and writes a copy of the

data from its internal latches to the memory cells.

The maximum Write time (tw) is shown in Table

16. and Table 17., but the typical time is shorter.

To make use of this, a polling sequence can be

used by the bus master.

The sequence, as shown in Figure 9., is:

– Initial condition: a Write cycle is in progress.

– Step 1: the bus master issues a Start condition

followed by a Device Select Code (the first

byte of the new instruction).

– Step 2: if the device is busy with the internal

Write cycle, no Ack will be returned and the

bus master goes back to Step 1. If the device

has terminated the internal Write cycle, it

responds with an Ack, indicating that the

device is ready to receive the second part of

the instruction (the first byte of this instruction

having been sent during Step 1).

11/26